ARM AXI

时间轴

2025-10-31

init

参考文档:

档:AMBA AXI and ACE Protocol Specificationi, issue H, part A & Part E

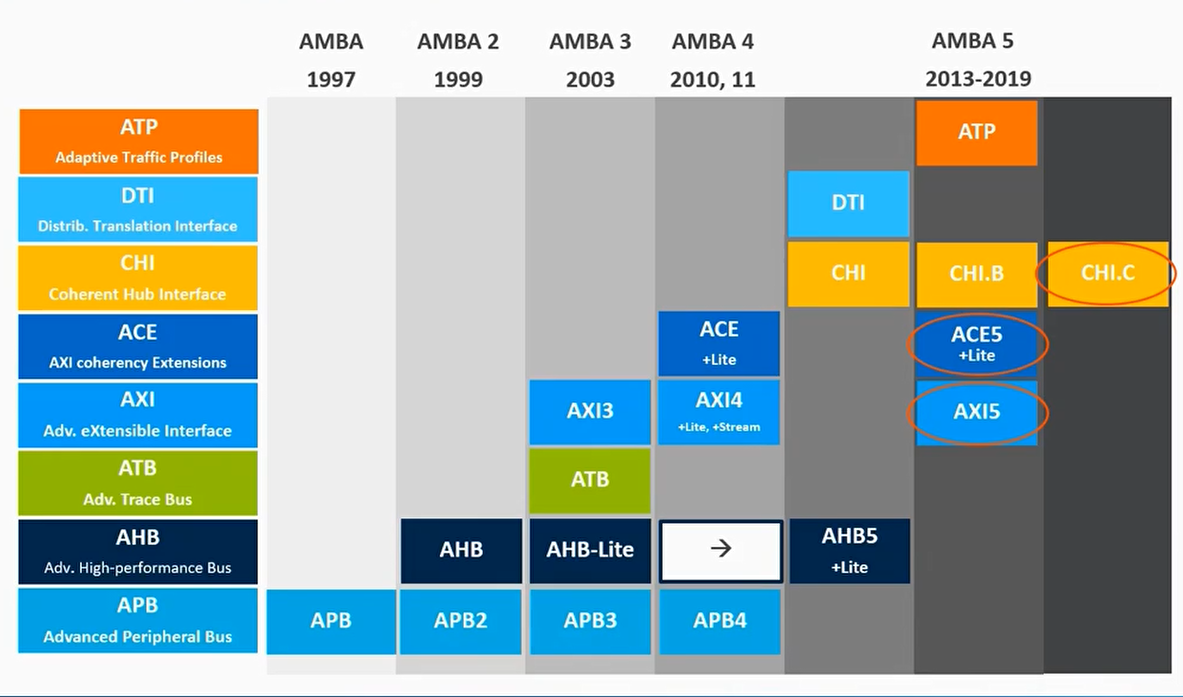

AMBA总线发展历史

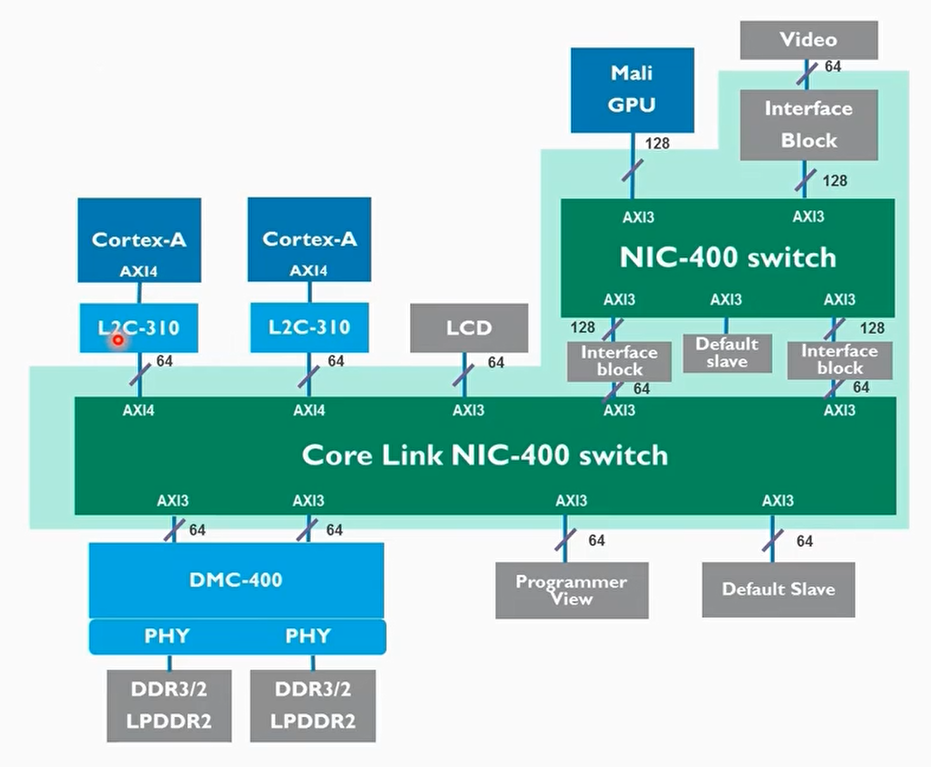

AXI总线的应用

AMBA总线发展历史

AXI基本概念:通道,传输,事务

什么是总线

总线由单个或者一组信号组成,传输数据或者控制信息

在总线上,发送方按协议规定的高点电平组合编码发送信息,接收方再解码

外部总线和内部总线

- 外部总线连接外围设备,可能外界干扰,连接器,PCB的损耗,信号完整性差

I2C,UART,SPI,PCIe,USB

- 内部总线用于SOC内部,在芯片内部走线,距离极短,很多干扰和信号完整性问题不需要考虑

AXI,UPI(intel)

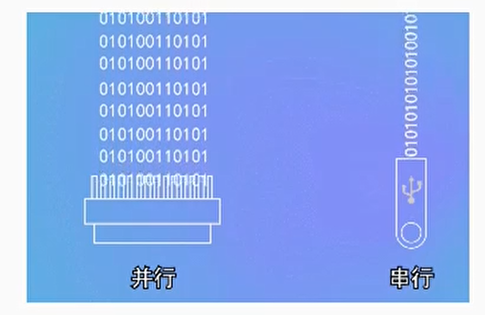

并行总线与串行总线

- 并行:多个数据同时传输,需要考虑数据的协同性,导致了并行传输的频率不能做的很高,容易干扰

- 串行:只有一条链路,把频率做的很高,提高传输速度

AXI总线的特点

- AXI总线是一个芯片内部的同步串行总线

- AXI总线的优点

- 高性能:高带宽(high-bandwidth),低延时(low-latency),高频率(High-frequency)

- 可灵活扩展总线位宽以及拓扑连接

- 兼容AHB和APB总线

- AXI总线的特点

- 独立的地址/控制和数据通道(seprate read & write channel)

- 支持burst传输

- 支持超前传输(multiple outstanding addresses)

- 在发送地址和数据阶段之间没有严格的时序要求(no strict timing between address and data phases)

- 支持乱序传输(out-of-order transaction completion)

- 支持非对齐数据传输(support unaligned data transfer)

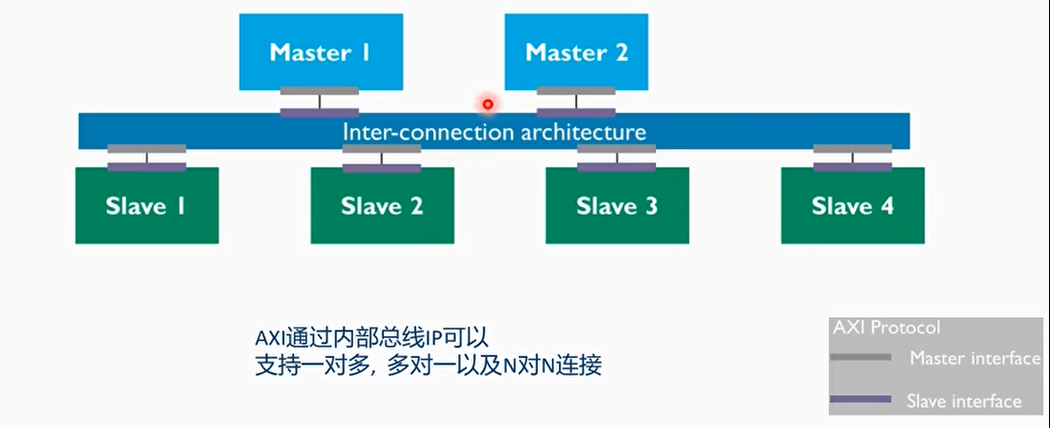

AXI拓扑

AXI使用主从机制

- 由master发起请求

- slave对请求进行应答

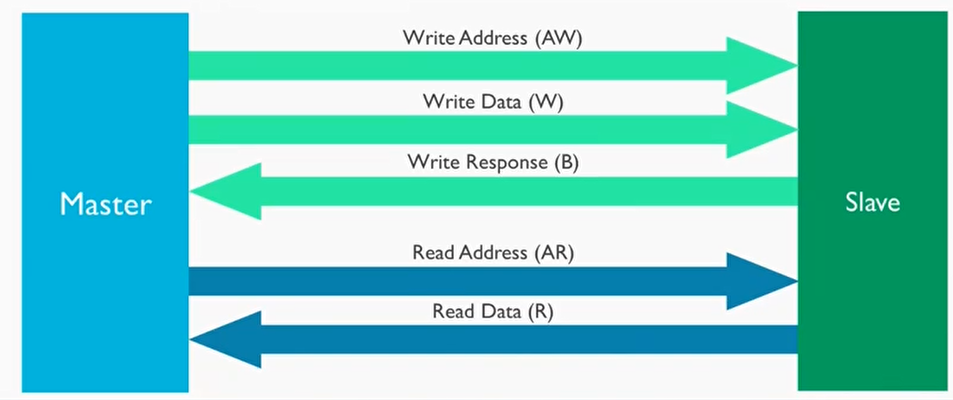

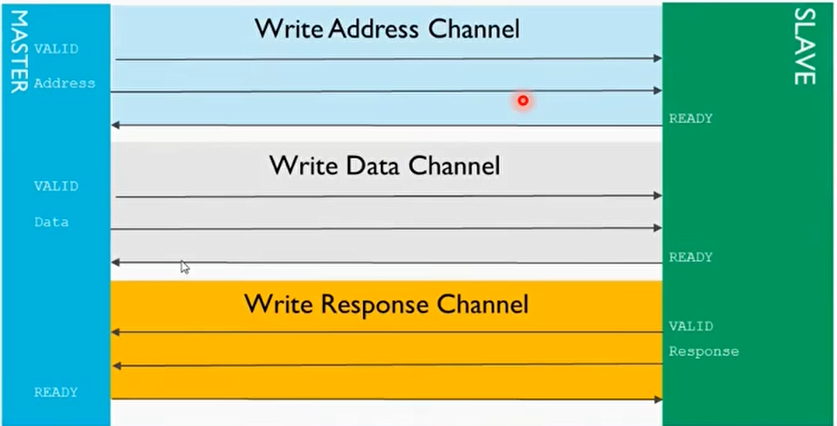

AXI通道

AXI定义了5个独立的传输通道(channel),提升bandwidth

- 读地址通道:AR

- 读数据通道:R

- 写地址通道:AW

- 写数据通道:W

- 写回应通道:B

每个channel不止一根信号线,而是一组信号线

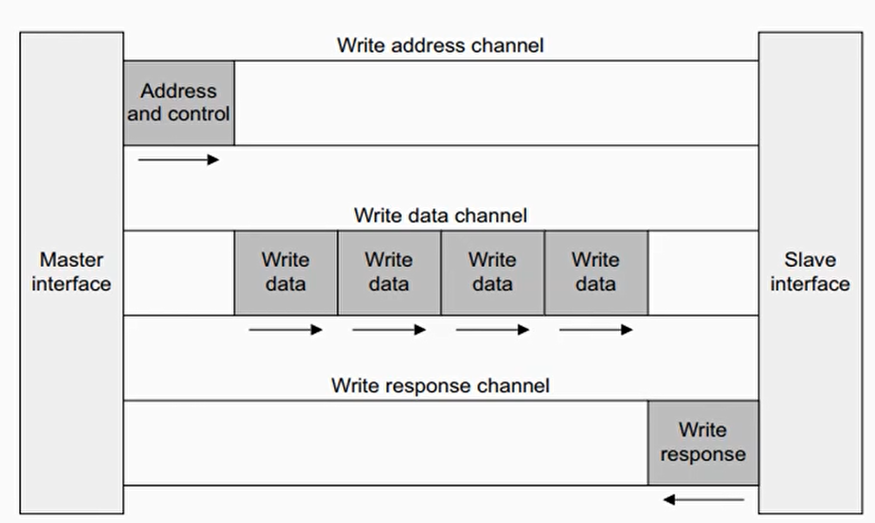

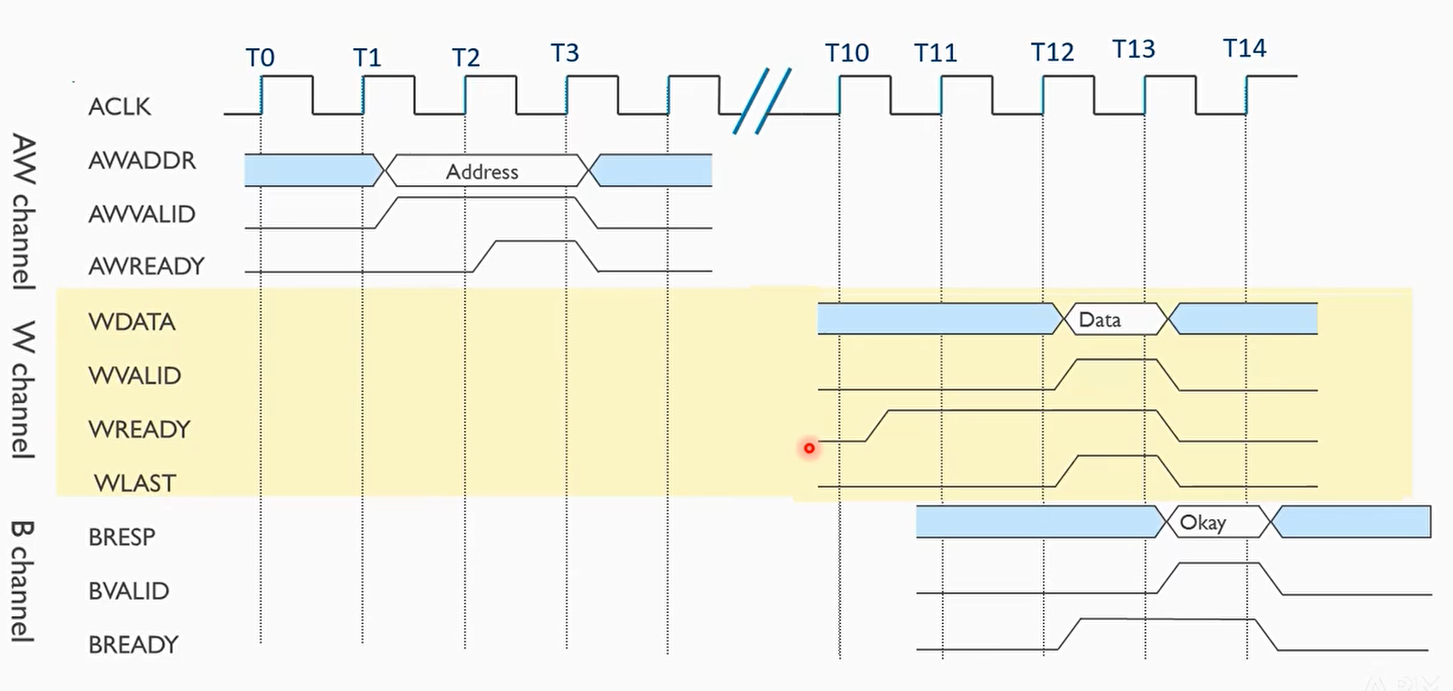

写传输事务

- 地址通道包含传输控制信息

- 传输事务步骤:

- Master通过write address channel发起写传输,包括地址和控制信息

- Master通过write data channel写数据给slave

- Slave通过write response channel回应

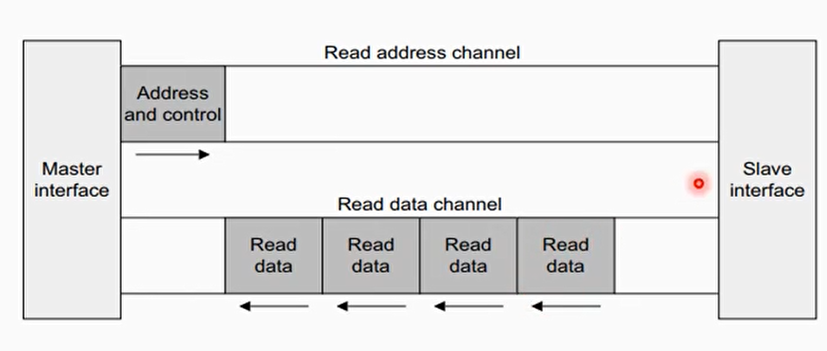

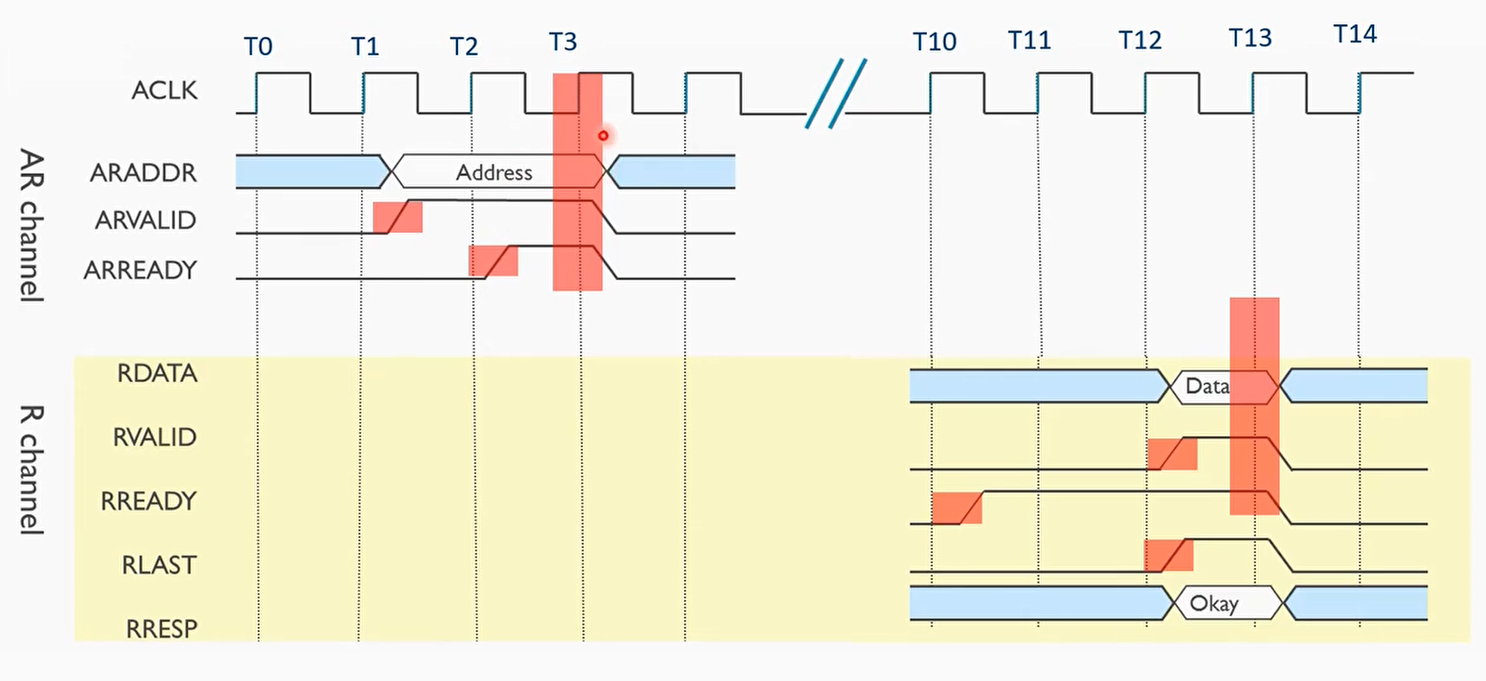

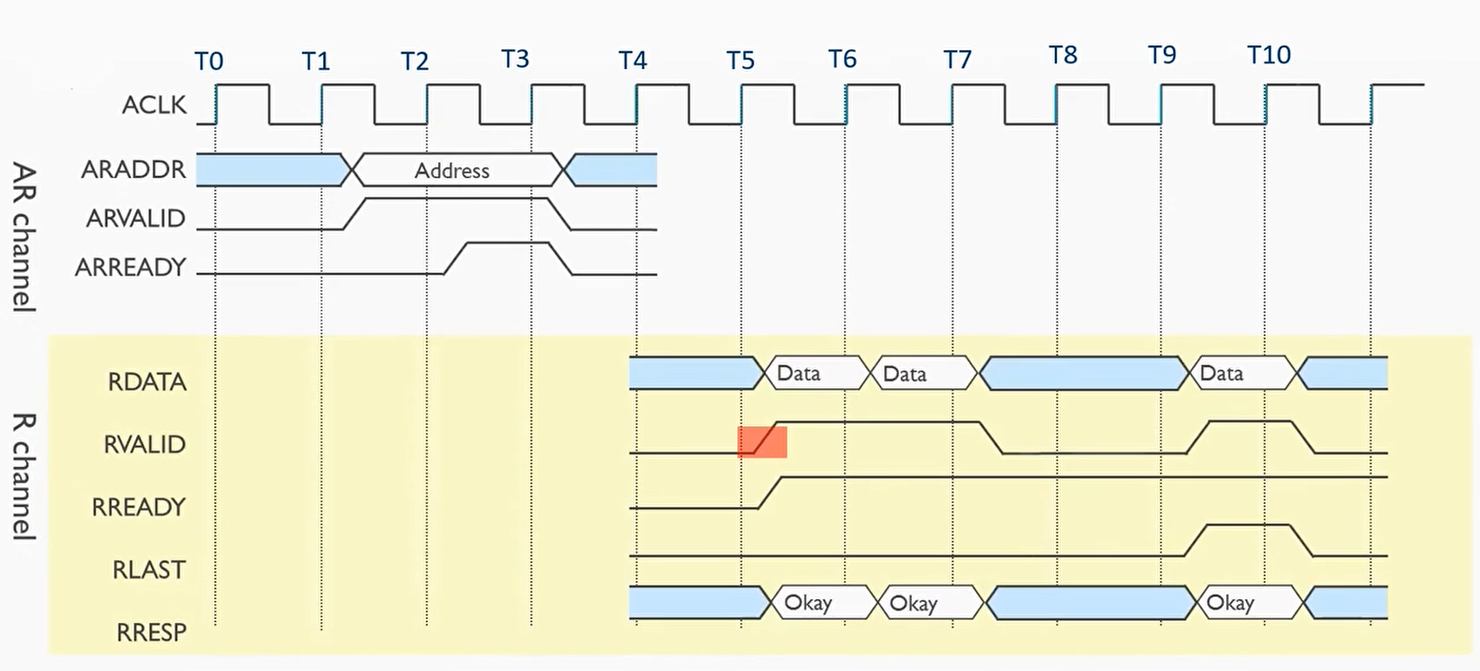

读传输事务

- Master通过read address channel发送地址和控制信息给slave

- Slave通过read data channel返回数据,回应信息包含在返回数据里

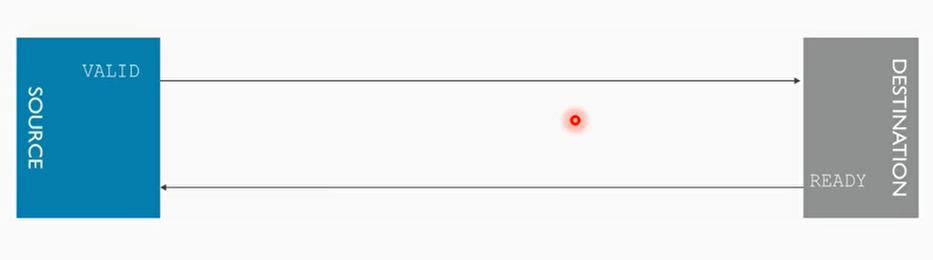

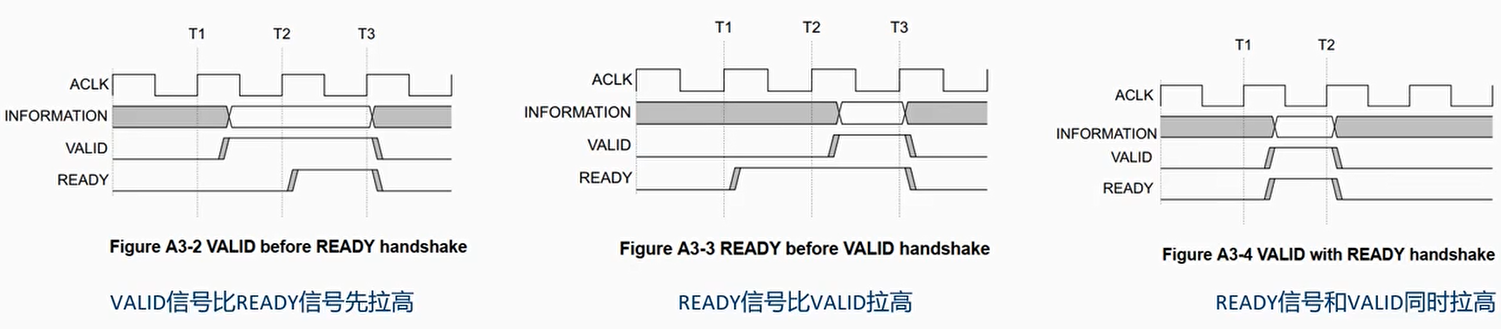

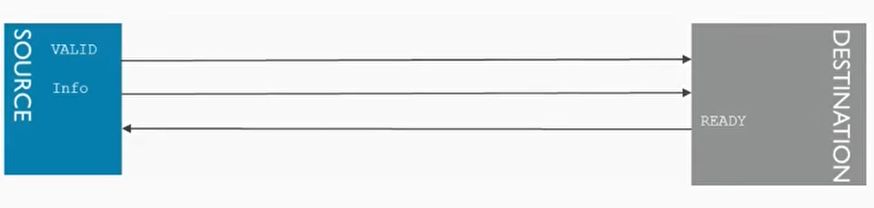

握手信号(Handshake process)

- 5个channel都使用相同的握手信号:VALID/READY handshake process

- source端产生VALID信号表明地址,数据,控制信息等已经ready了

- destination端产生READY信号表明它开始接受信息了。

只有READY和VALID信号同时有效时才握手

传输transfer和事务transaction的区别

Transfer

只有一次的握手过程,传输一次数据

transaction

有多次的握手信号,由多次的transfer来组成

以write为例,通过write address channel传递地址和控制信息。然后通过write data channel来传输数据。最后通过write response channel来回应。

一共有3个transfer

例子:Write transaction: single data item

例子:Read transaction:single data item

例子:Read transaction:multiple data items

通道信号和事务结构

写地址通道(write address channel)的信号线

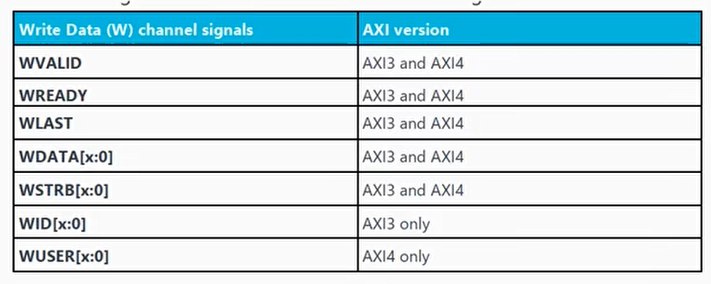

写数据通道(write data channel)的信号线

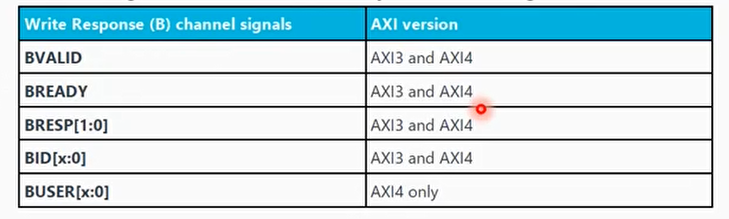

写回应通道(write response channel)的信号线

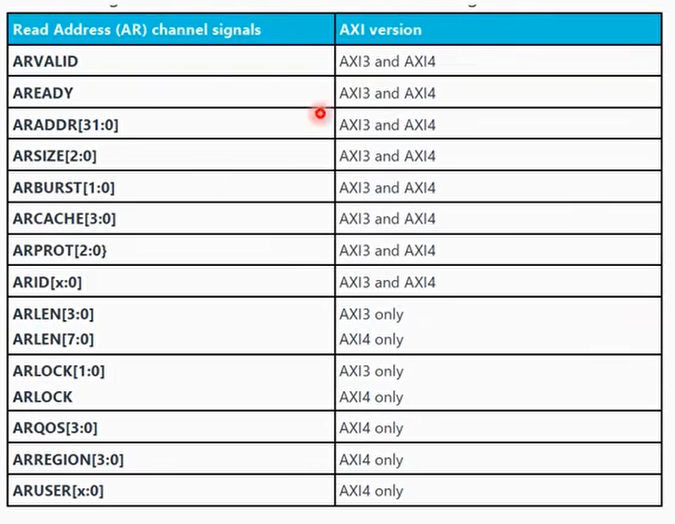

读地址通道(read address channel)的信号线

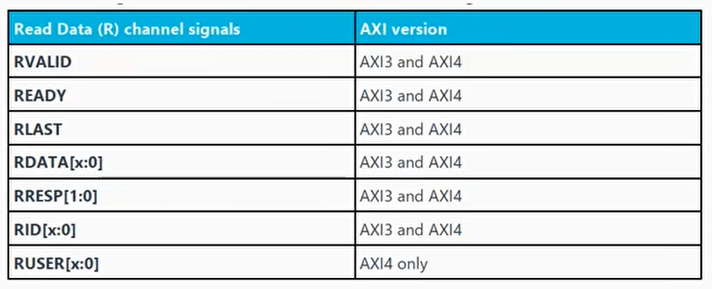

读数据通道(read data channel)的信号线

Transaction structure

- 一次burst中包括多少个传输transfer

- AXI3最多包含16个transfer:Burst_Length = AxLEN[3:0] + 1

- AXI4最多包含256个transfers:Burst_Length = AxLEN[7:0] + 1

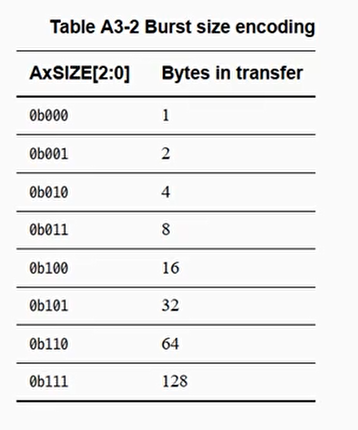

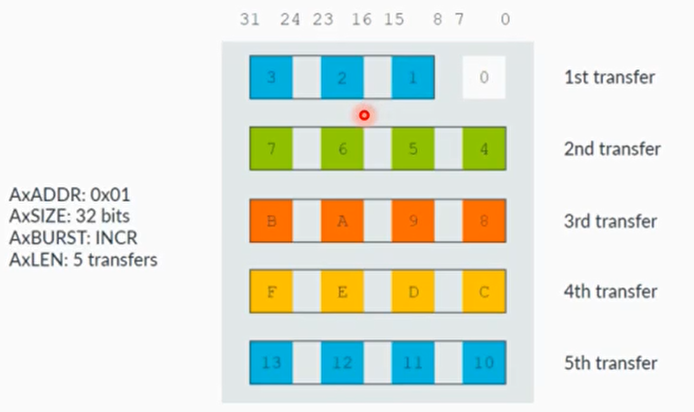

- AxSIZE:表示一个transfer传递多少个字节,最大128个字节

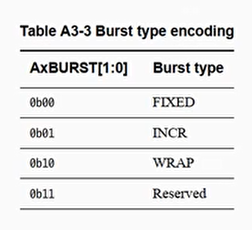

AxBURST:表示burst类型

FIXED:固定地址模式,应用于FIFO

INCR:地址递增模式,应用于RAM

slave递增地址,支持1~256个transfers,支持unaligned transfer

WRAP:地址递增,达到上限后绕回,应用于Cache

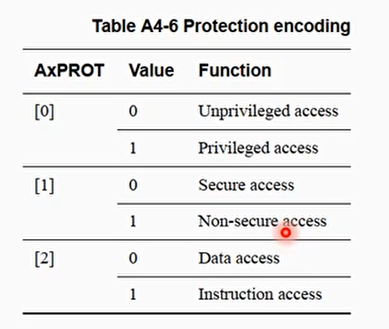

访问权限(Access permissions)

- ARPROT[2:0]:表示读事务的访问权限

- AWPROT[2:0]:表示写事务的访问权限

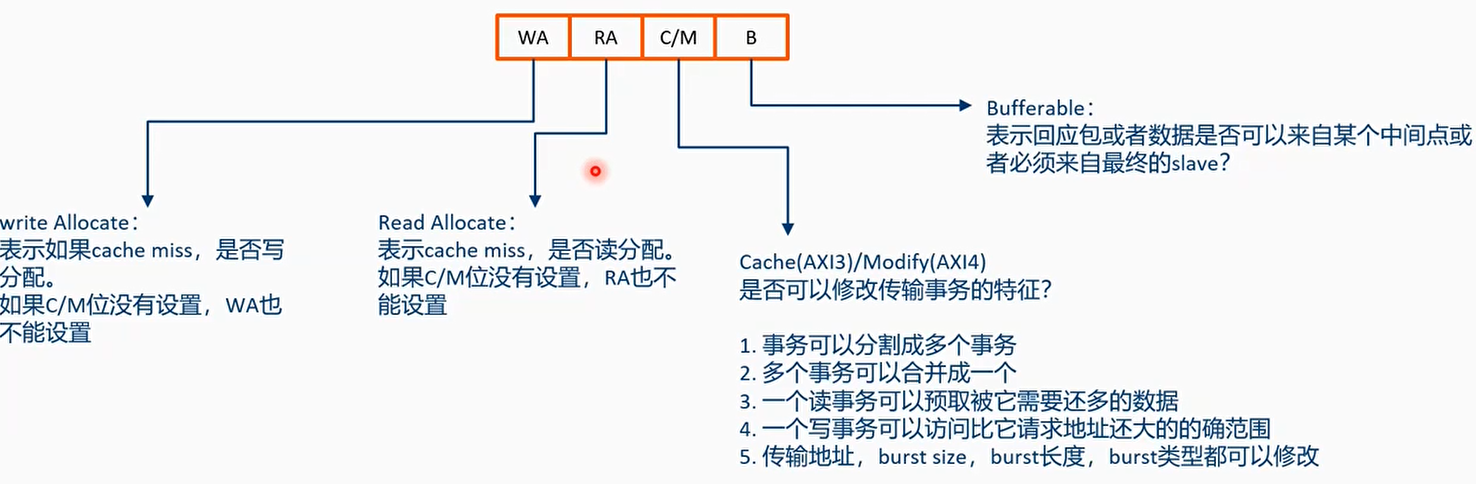

高速缓存的支持

- 传输过程中可以利用各种缓存

- 系统各级高速缓存,例如L2/L3 cache

- 系统总线内部的缓存(with the iterconnect)

- AxCACHE[3:0]:表示高速缓存属性

回应包(response structure)

RRESP[1:0],for read transfers

BRESP[1:0],for write transfers

OKAY:表示normal access成功或者exclusive access has failed

EXOKAY:表示exclusive access成功

SLVERR:slave error

DECERR:解码错误

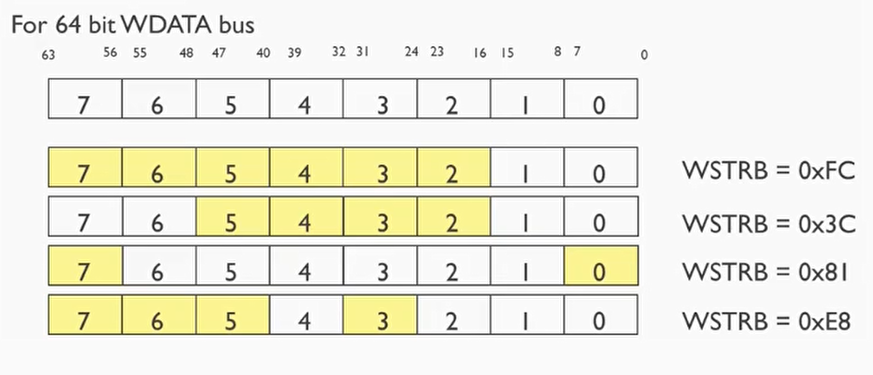

Write strobes

- WSTRB[n:0]:表示WDATA上的数据是否有效,一个bit表示一个字节

- 主要是为了支持不对齐访问

QoS信号

- AXI总线提供额外的信号线来支持quality of service

- AWQOS:4-bit QoS,在每个写事务的write address channel中

- AWQOS: 4-bit QoS, 在每个读事务的read address channel中

- 0表示最低优先级,F表示最高优先级

- 一般系统总线IP提供寄存器来配置每个master的QoS

通道依赖关系

- 依赖关系1:在AWVALID有效之前,WVALID先设置有效

- AWVALID表示write address channel有效

- WVALID表示write data channel有效

- 写地址有效之前,可以先把数据发送出去

- 依赖关系2:在BVALID有效之前,必须发送WLAST

- BVALID表示write response channel有效

- WLAST表示时事务中最后一个transfer

- 在写回应包发送之前,所有的写data和地址address必须发送完成

- 依赖关系3:在ARADDR发送完成之前,RVALID不能有效

- ARADDR表示读事务的第一个transfer的地址

- RVALID表示read data channel有效

- 如果地址没有发送完成,不应该看到有读数据返回

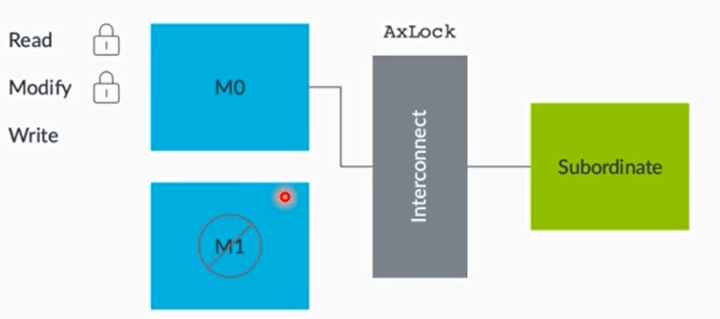

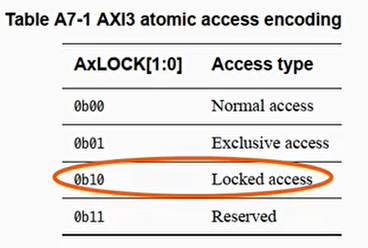

lock access and exclusive access

Locked accesses

- Locked access只在AXI 3协议中,AXI 4已经遗弃

- AXI 3和AXI 4里有AxLOCK信号线

- AXI 3中,Locked access类似锁住总线

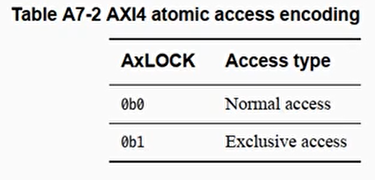

Exclusive access

Exclusive access 比 Locked access 更高效,不需要锁住总线,其他master可以同时访问总线

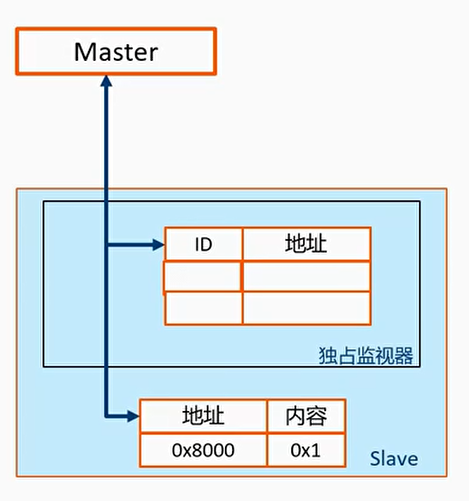

需要在slave端实现exclusive monitor来协同完成exlusive access

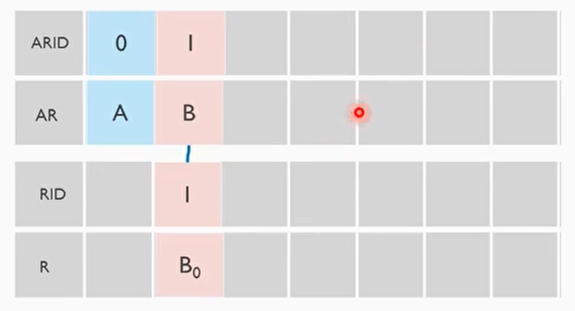

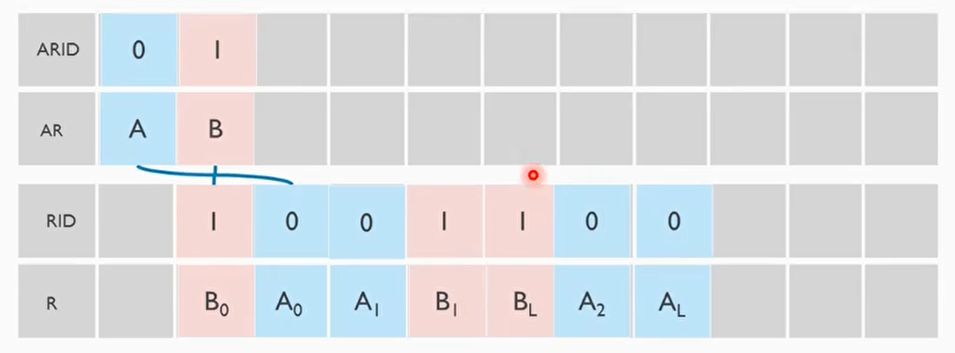

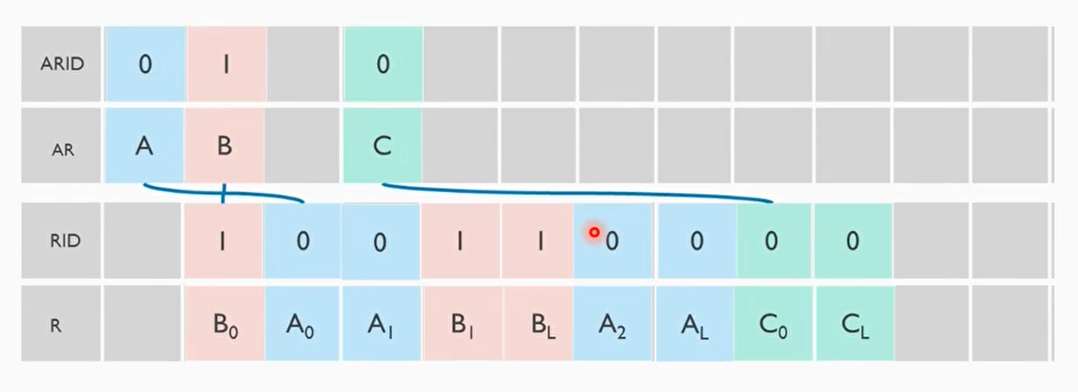

ARID 读事务的ID

AWID 写事务的ID

访问流程

- master发起exclusive读。Slave的exclusive monitor把ARID,地址以及数据填入到表里面。

- master对同一个地址发起exclusive写操作。exclusive monitor查表并比较AWID和ARID是否一致

- 回应

- EXOKAY(成功),如果这期间没有其他master对这个地址进行写入,那么exclusive写操作就成功

- OKAY(失败),如果这个期间有其他master对这个地址进行写入,那么exclusive写失败

例子:独占访问失败

操作序列:

- Master往0x8000地址发起第1次的exclusive read操作

- Master往0x8000地址发起第2次的exclusive read操作

- Master往0x8000地址exclusive地写入0x3->成功

- Master往0x8000地址exclusive地写入0x5->失败

前三步操作:

Exclusive write时有相同ID的读事务,所以写入成功

当exclusive write成功之后,独占监视器会把这个地址和ID相关的所有entry从这个table里删掉

Exclusive Write时查表时没有相同ID的读事务,所以失败

事务的次序transaction ordering

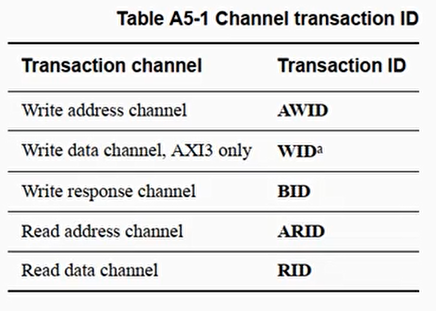

AXI transaction ID

- AXI为每个事务通道有一个独立事务ID

- 所有的transfer必须有一个ID

- 在同一个事务的transfer有相同的ID

- 事务ID是为了out-of-order

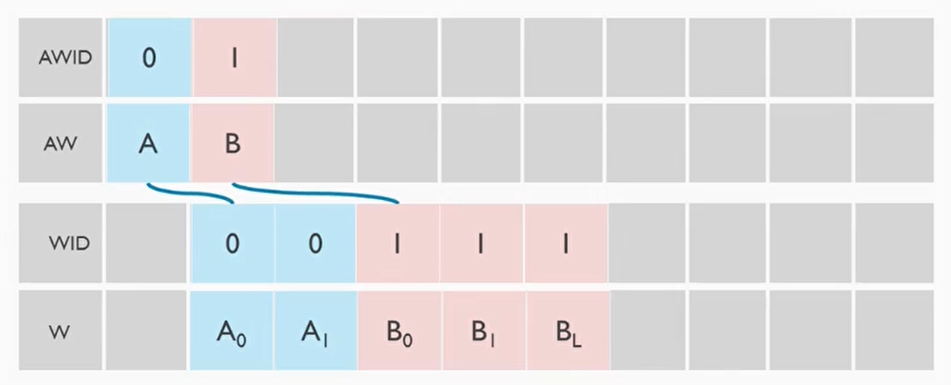

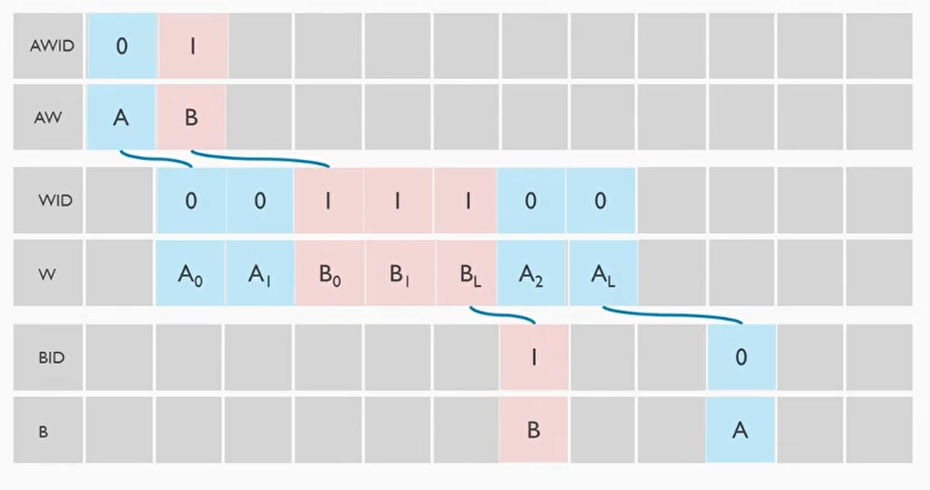

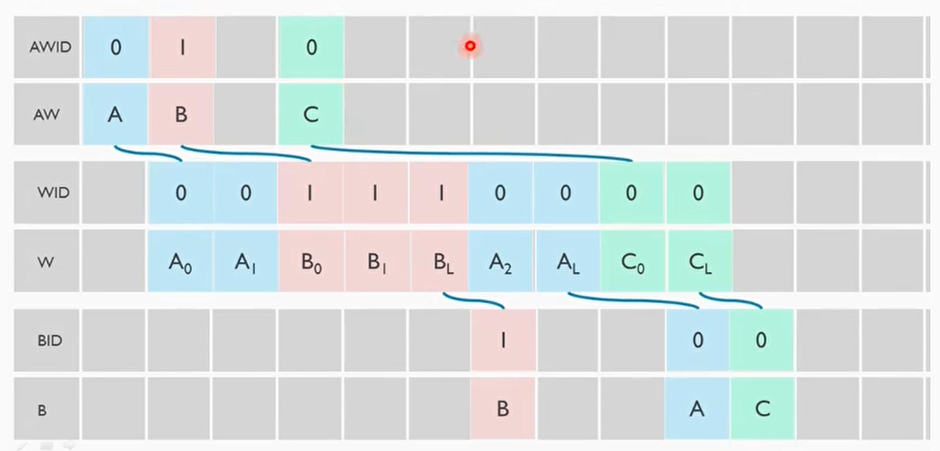

写事务次序规则

- 写事务次序规则1:在write data channel写数据的次序必须和write address channel中的地址传输次序一致(data must follow the same order as address transfers)

在write address channel是先发送A地址,然后再发送B地址,所以在write data cache中,先发送A数据,然后再发送B的数据

- 写事务规则2:不同ID的写事务之间可以任意次序完成(data for different transation IDs can be interleaved)

事务B比事务A先完成,尽管事务A比事务B先执行

- 写事务规则3:相同ID的写事务,按照顺序执行和按照顺序完成(data with the same ID must follow in the order as issued)

事务B和事务A,C的ID不同,事务B可以任意次序完成。事务A和C使用相同的ID,那么必须事务A先完成,然后才是事务C

读事务次序规则

- 读事务次序规则1:在read data channel不同的ID的事务可以任意次序(data for different IDs has no ordering restrictions)

尽管在read address channel中事务B比事务A晚发送地址,但是,事务B可以比事务A先读取数据

- 读事务规则2:不同ID的事务的传输在read data channel可以交织地读(data with different transaction IDs can be interleaved)

事务A和事务B交织地读数据

- 读事务规则3:相同ID的读事务必须按照顺序完成(data with same ID must follow in the order as issued)

事务A和C有相同的ID,事务A比事务C先发送,那么事务A也必须比事务C先完成

非对齐地址访问

- AXI总线支持非对齐地址访问,使用byte strobes机制

从0x1地址开始,先传输3个字节,随后就对齐了地址

AXI-Lite总线

AXI4-Lite总线介绍

- AXI4-Lite不支持burst模式,或者burst长度为1

- AXI4-Lite支持数据位宽32bit或者64bit

- AXI4-Lite所有访问都是Non-modifiable,Non-bufferable

- 不支持exclusive access

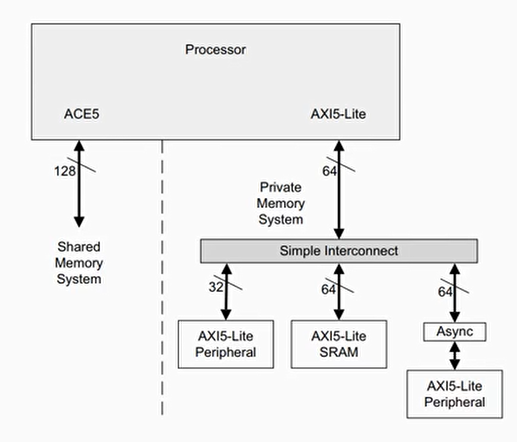

AXI5-Lite总线介绍

- AXI5-Lite在AXI4-Lite基础上放宽了数据位宽和事务传输次序的要求

- AXI5-Lite的特点

- 不支持burst模式,或者burst长度为1

- 所有访问都是Device and Non-bufferable

- 不支持exclusive access

- 当请求具有不同的id时,允许对响应进行重排序

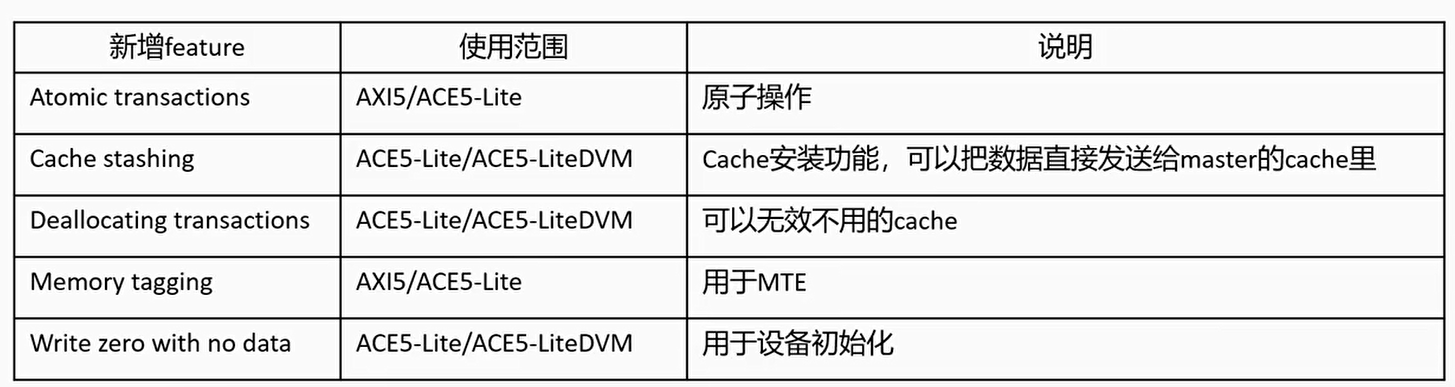

AXI5/ACE5新增的功能

总结

- AXI总线定义了5个独立的通道,每个通道由一组信号线组成

- AXI总线定义了传输事务的数据结构和属性

- Burst的数量

- Transfer的大小

- Burst类型

- 回应包

- 高速缓存支持

- 访问全新啊

- QoS信号

- 支持exclusive access

- 通过事务ID来支持乱序传输

- 支持非对齐访问