ARM ACE

时间轴

2025-10-31

init

参考文档:

ACE

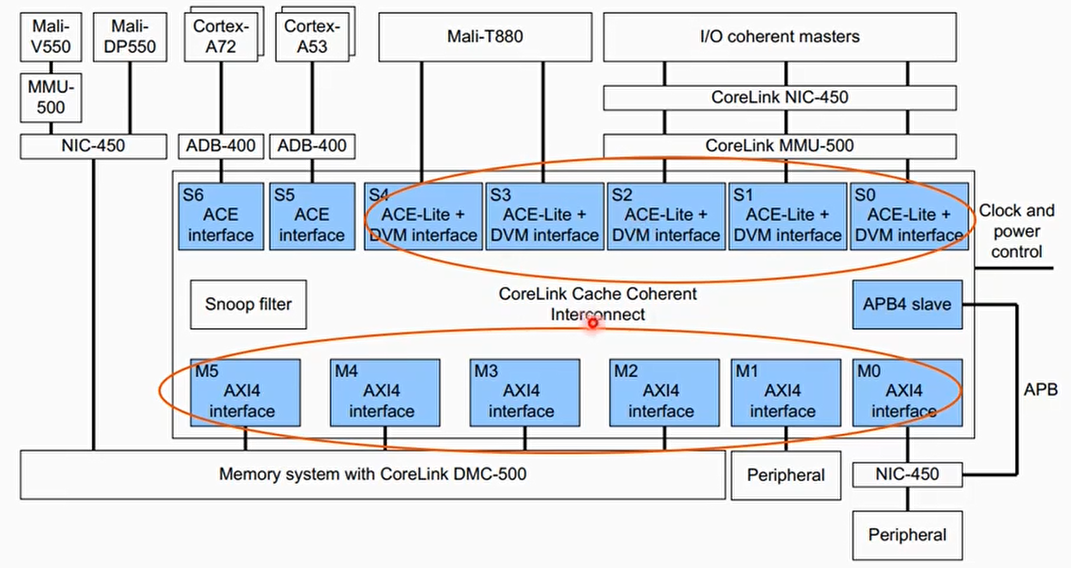

- ACE(AXI Coherency Extensinos)是基于AXI总线的硬件缓存一致性解决方案

- 关注系统级的缓存一致性

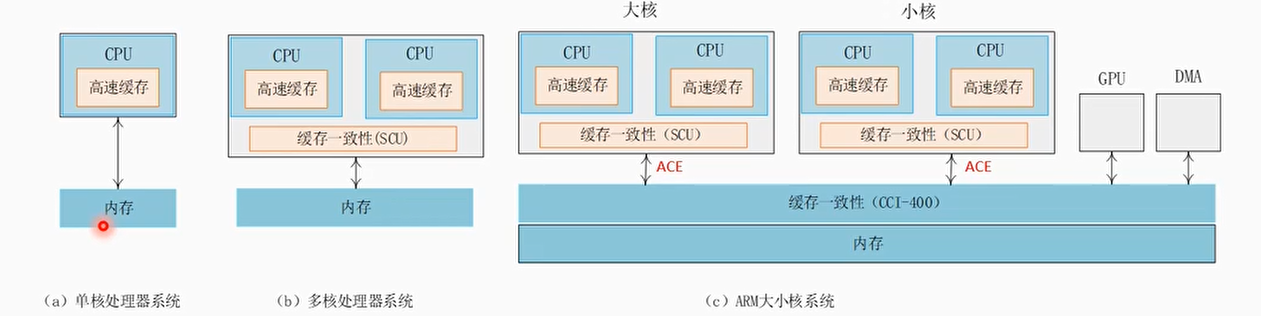

最早是从大小核架构的Cortex-A15/A7开始支持ACE接口

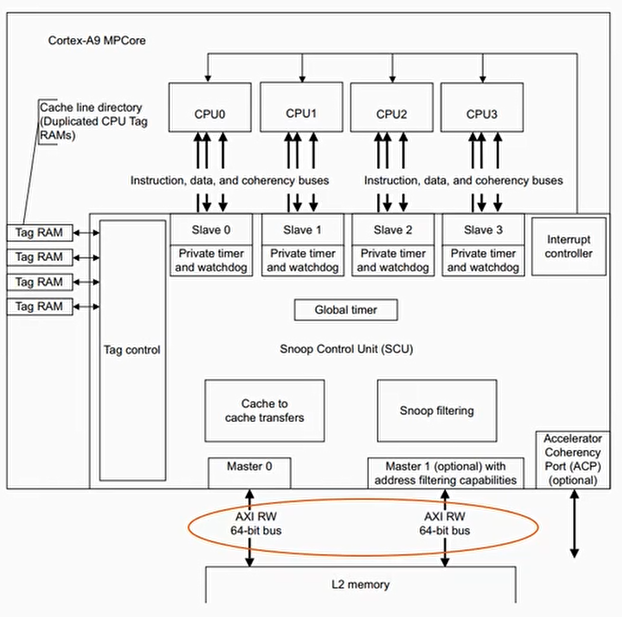

Cortex-A9不支持ACE接口,通过AXI接口连接到L2和Memory

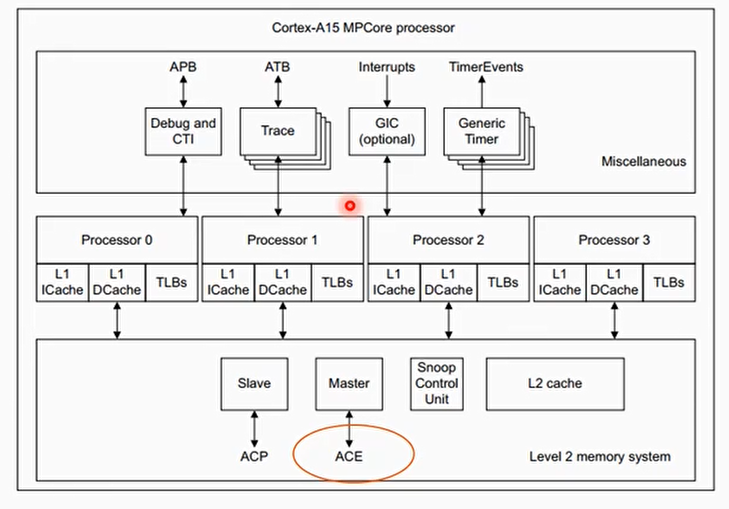

Cortex-A15支持ACE接口,大小核架构下,大cluster和小cluster通过ACE连接到CCI总线上

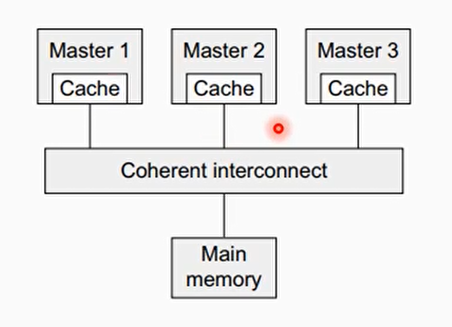

- 三个master,都有本地cache。ACE允许对同一个内存地址这三个master都有相同的cache拷贝

- 这里master一般指的是CPU cluster或者具有cache的控制器

- ACE保证对一个给定的地址,所有master都能访问到正确的数据

ACE关注带cache的master之间的系统缓存一致性问题,例如Cortex-A72族与Cortex-A53族

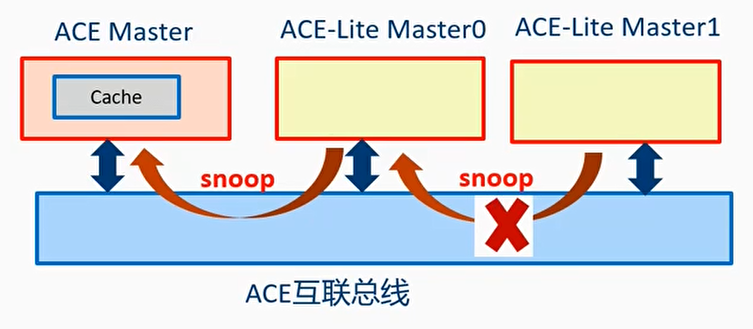

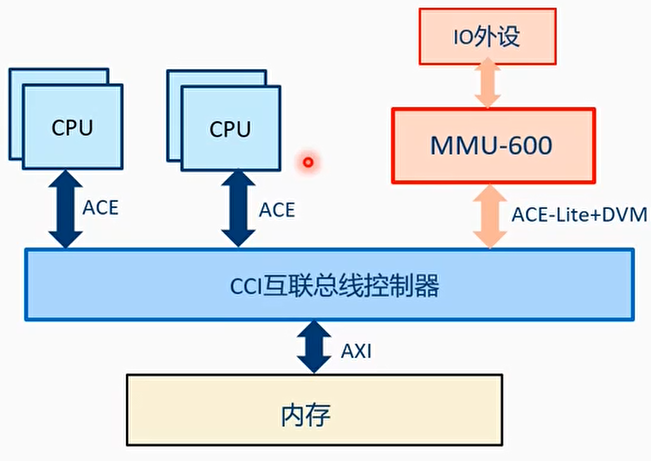

ACE-Lite用于连接不带cache的硬件IO设备,但是这些设备需要访问系统缓存一致性的内存,例如GPU,SMMU等,DVM interface用于broadcast TLB invalidation

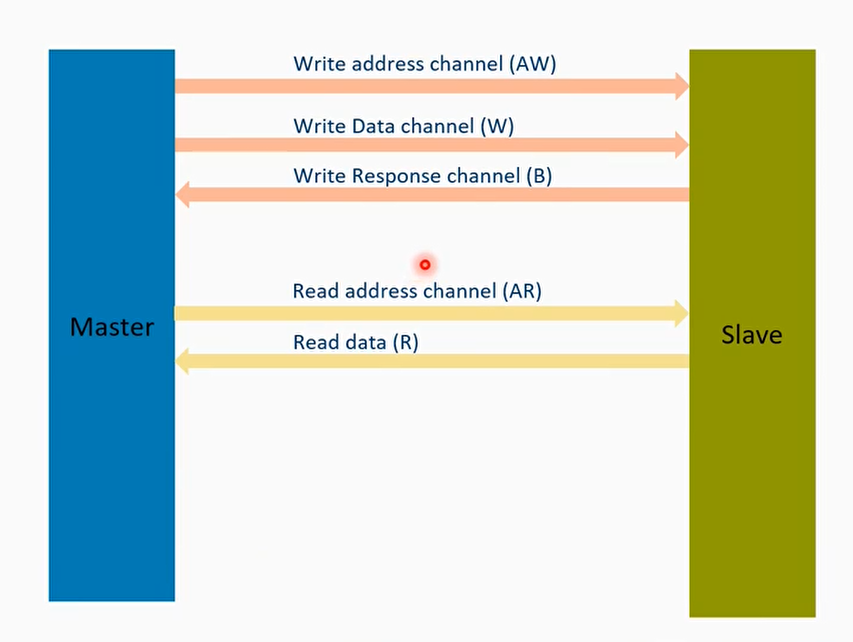

ACE实现的基本思路

- 需要实现一种snoop机制来保证多个master的cache一致性

- 在AXI的基础上新增信号线以及新的传输事务来实现snooping

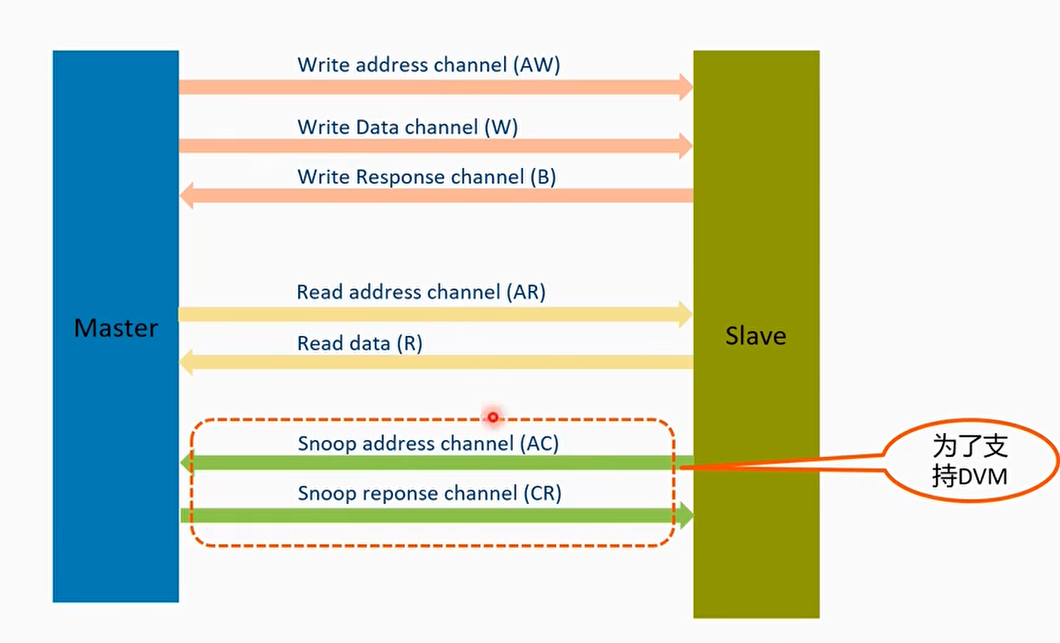

- 在AXI基础上新增新的传输通道

- 实现5个state的cache状态转换机制(因为有的master使用MESI有的master使用MOESI等)

- ACE支持memroy barrier(ACE5移除)

- ACE支持exclusive access

- ACE支持DVM

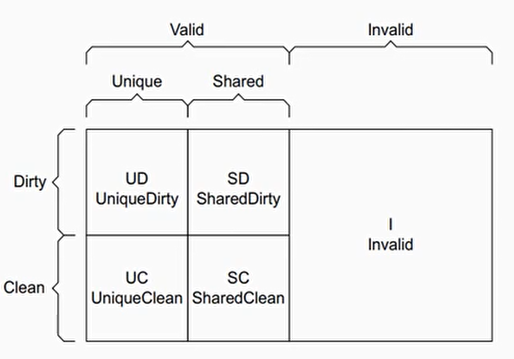

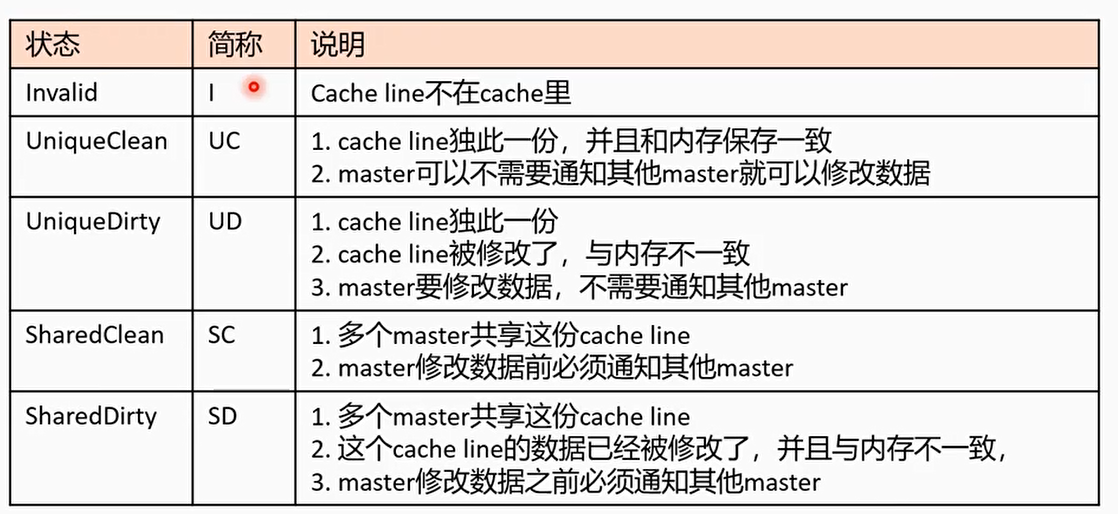

ACE的状态机

valid:cache line有效

invalid:cache line无效

unique:表示这个cache line是独占,只有当前master有

shared:多个master都有这个cache line的拷贝

clean:表示cache line的内容和内存一致

dirty:cache line的内容和内存不一致,需要稍后写回到内存

类似MOESI协议

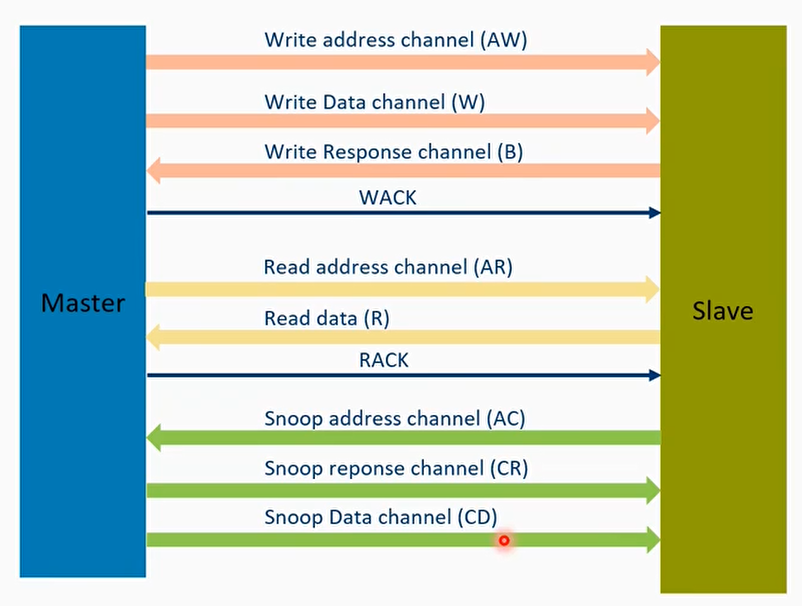

ACE新增的channel

ACE新增的信号

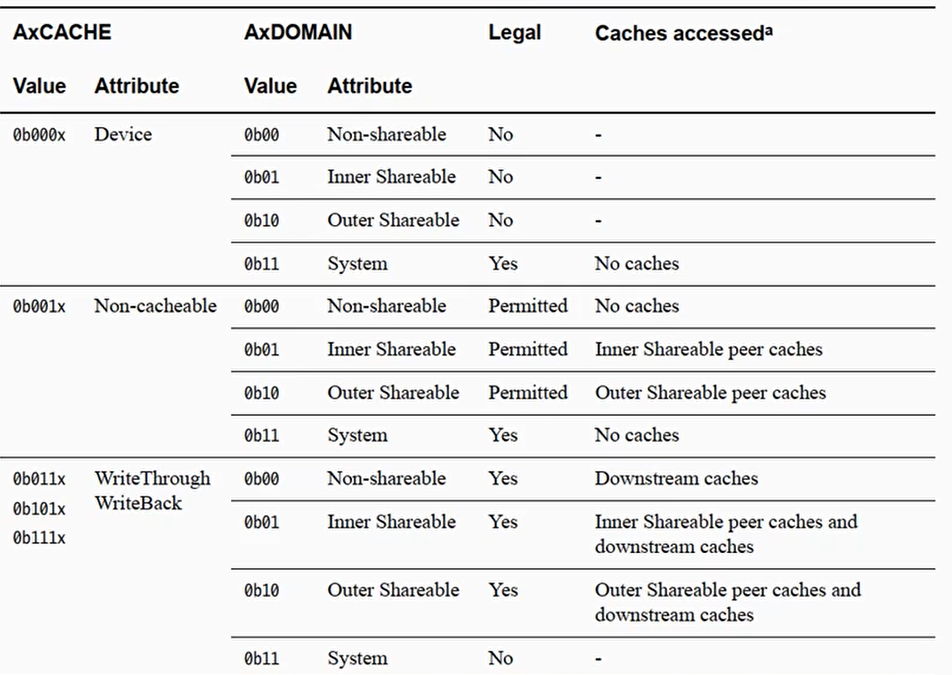

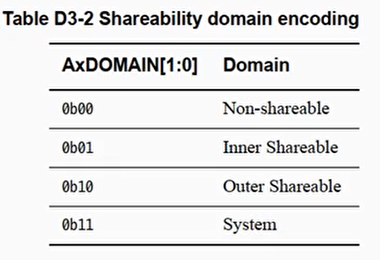

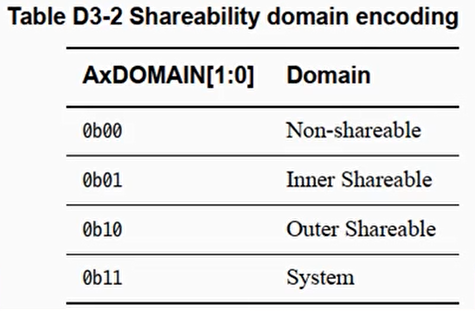

- AxDOMAIN:用来指示shareability domain:

- Nono-shareable,Inner Shareable,Outer Shareable,System

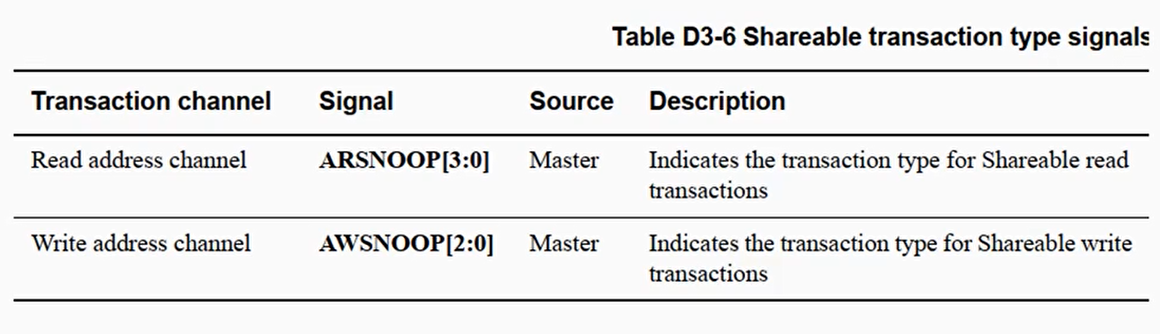

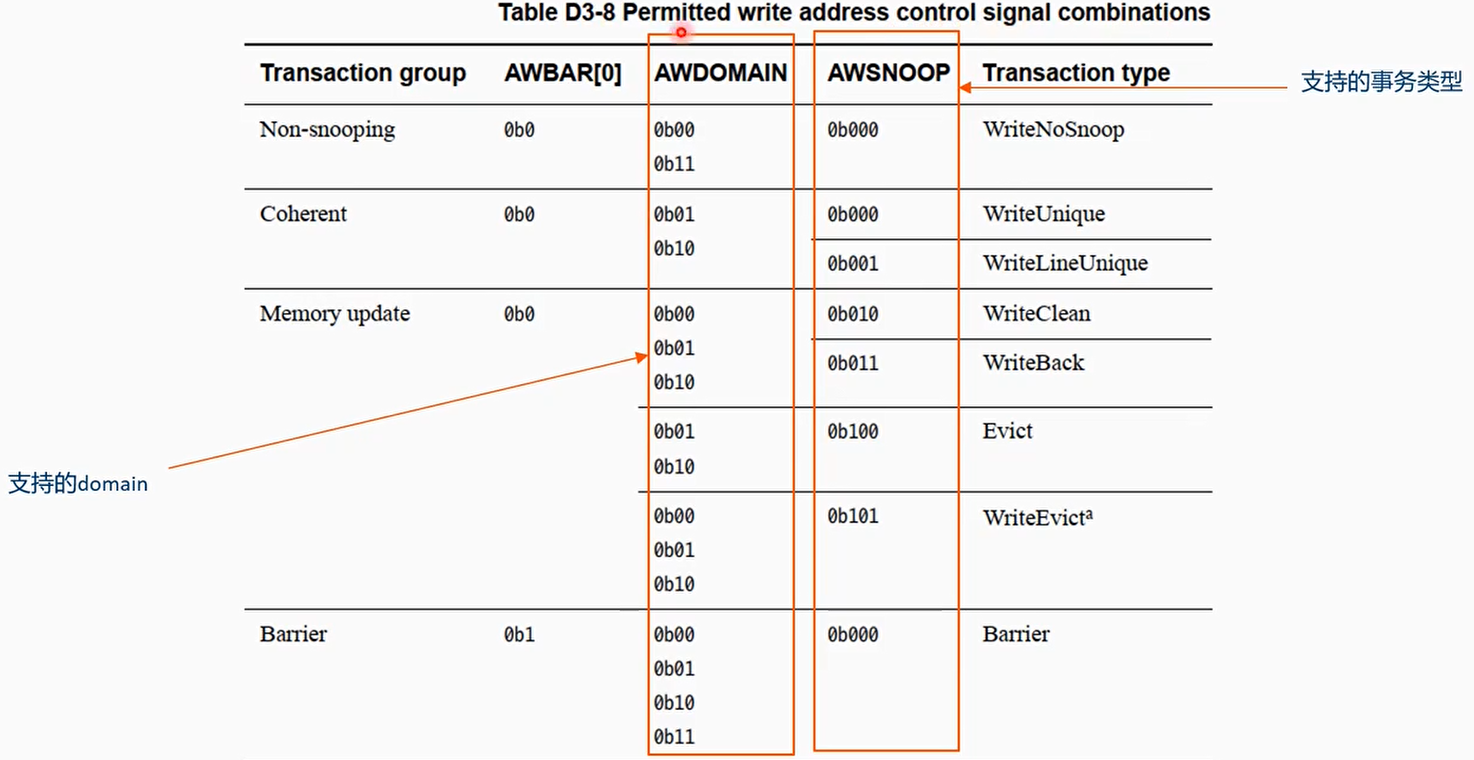

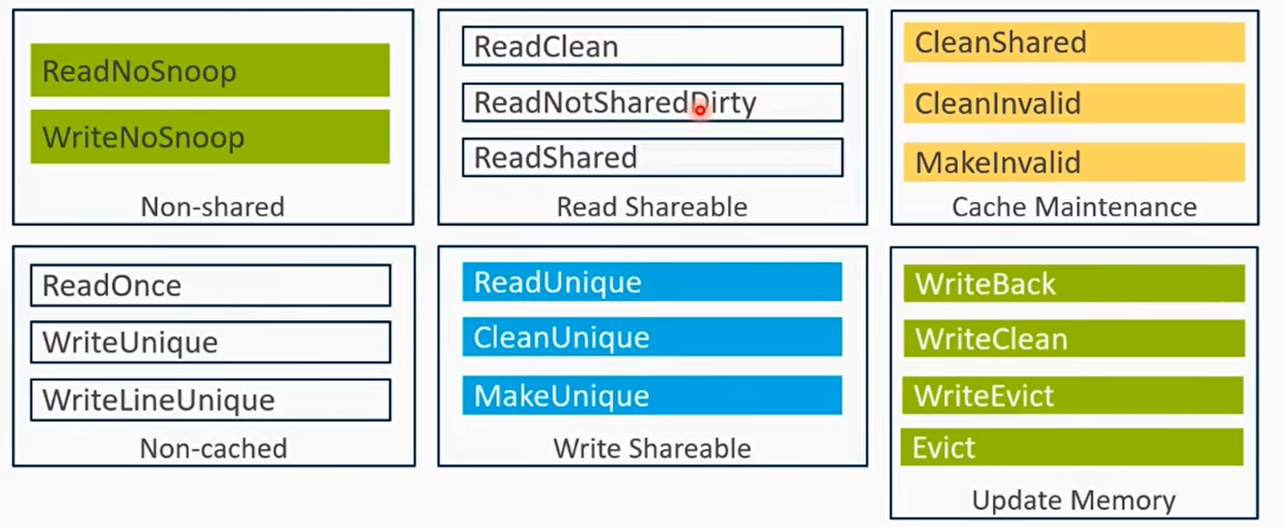

- AxSNOOP:用来指示snoop传输事务类型

- AxBAR:表示发起一个barrier事务(ACE5移除)

- AWUNIQUE:用于优化写传输事务的cache状态转换

AxDOMAIN信号线

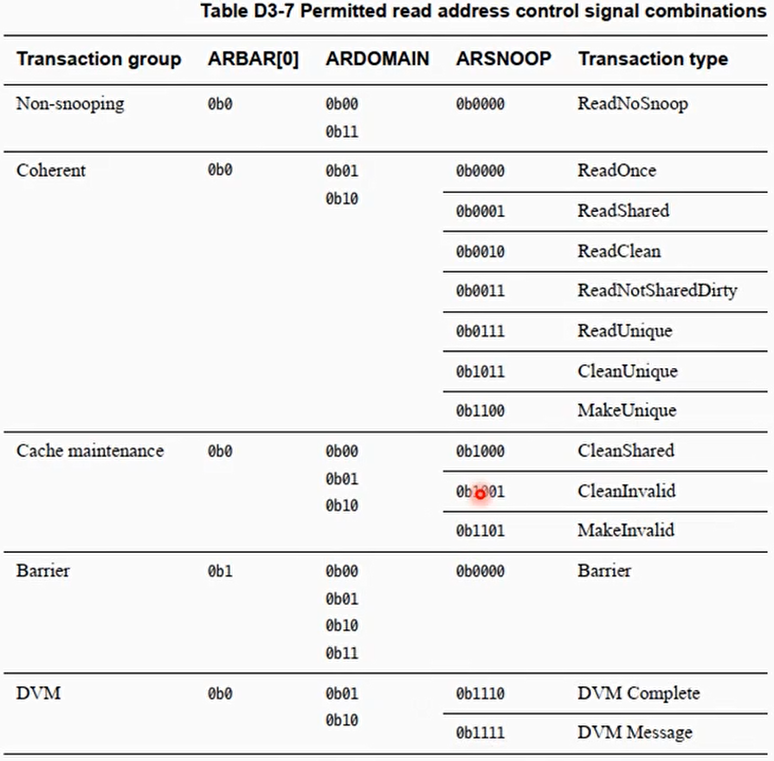

AxSNOOP信号线

- AxSNOOP:用来指示snoop传输事务类型

- Non-snooping

- Coherent

- Memory update

- Cache维护

- DVM

- barrier

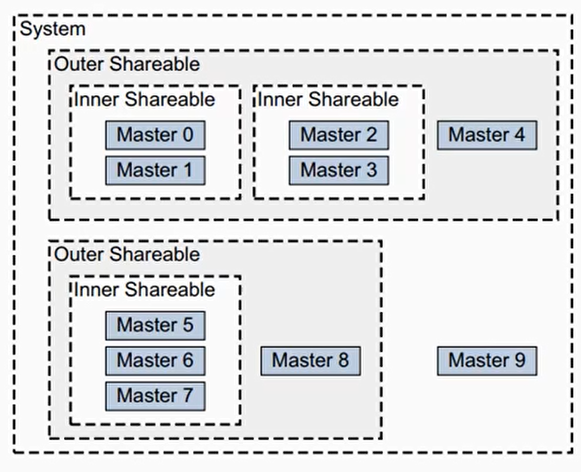

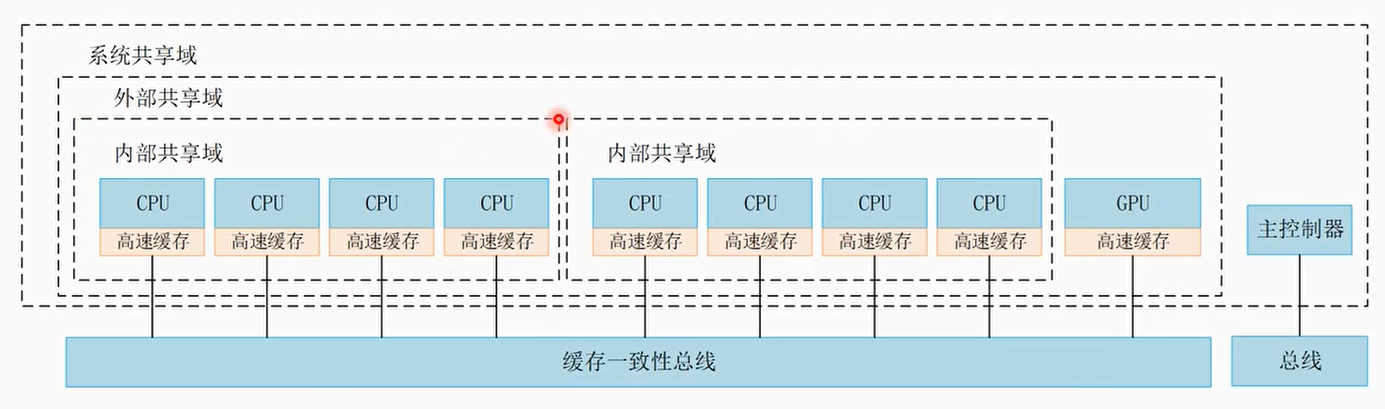

shareability domains

在发起coherency或者barrier传输事务之前,master用来确定这些事务传输应该发送给哪些master

- Coherent事务:确定哪些master可能有这个数据的拷贝,用来发送snoop事务

- Barrier事务:确定与哪些master会建立排序的关系,以及barrier事务要传播到多远

支持4种shareability域:

- Non-shareable:仅仅包含一个master

- Inner Shareable

- Outer Shareable

- System

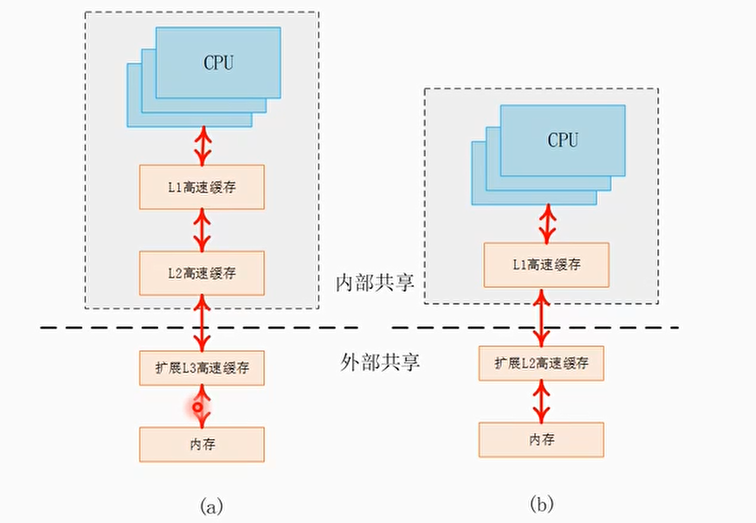

- Inner share:通常是指CPU内部集成的高速缓存,它们最靠近处理器核心,例如Cortex-A72核心内部可以集成L1和L2高速缓存

- Outer share:通过系统总线扩展的高速缓存,例如连接到系统总线上的扩展L3高速缓存

Snoop事务

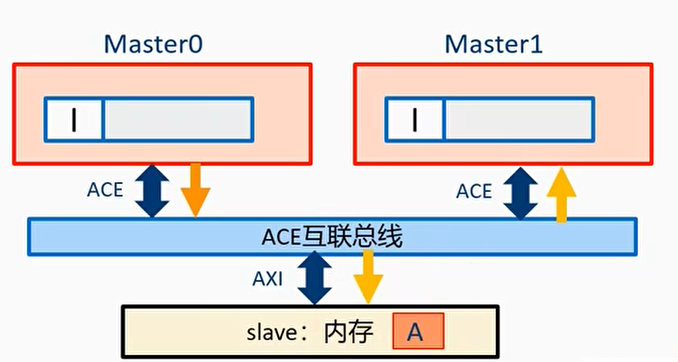

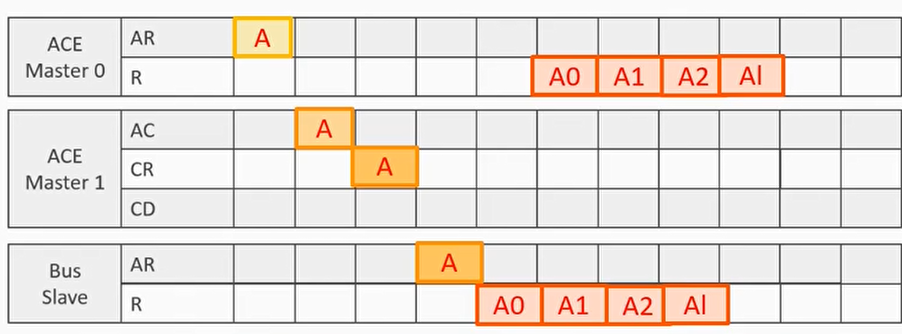

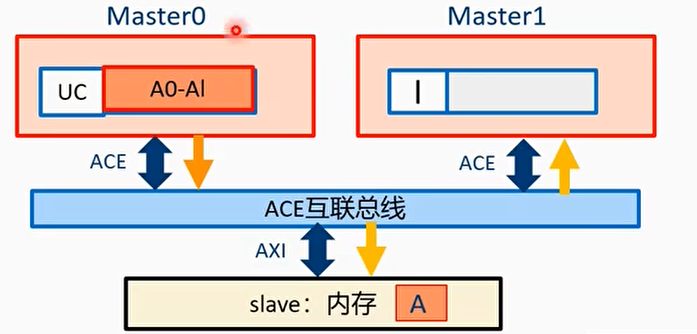

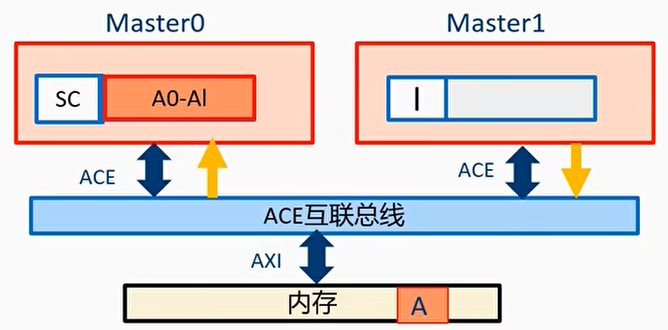

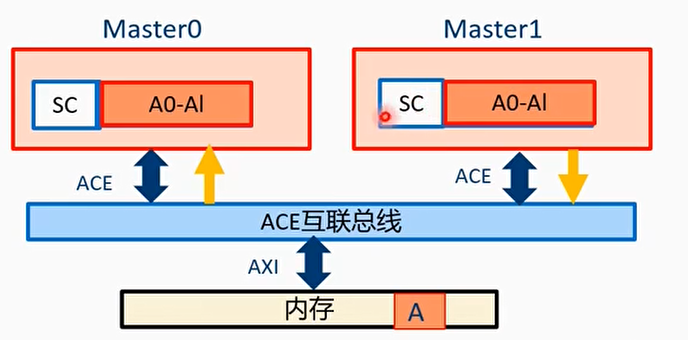

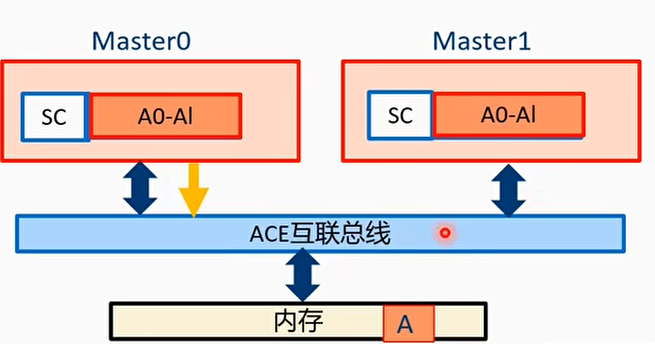

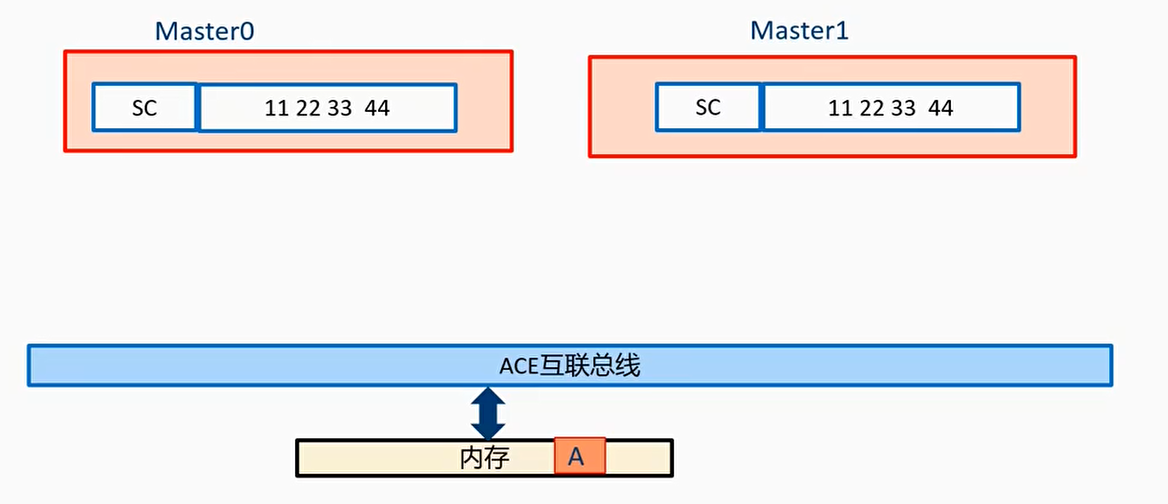

例子1:shareable read and miss

最终:

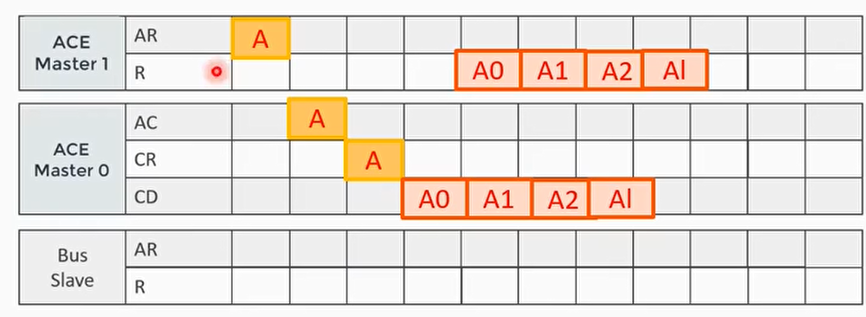

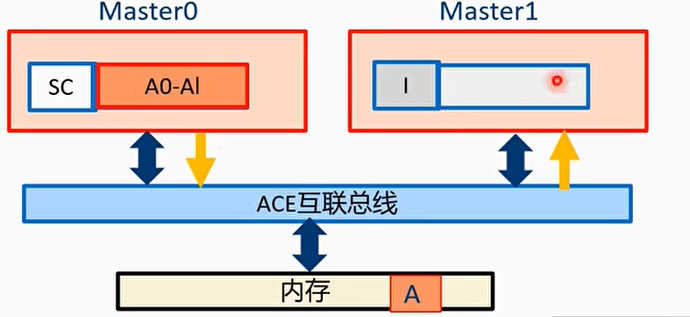

例子2:shareable read and hit

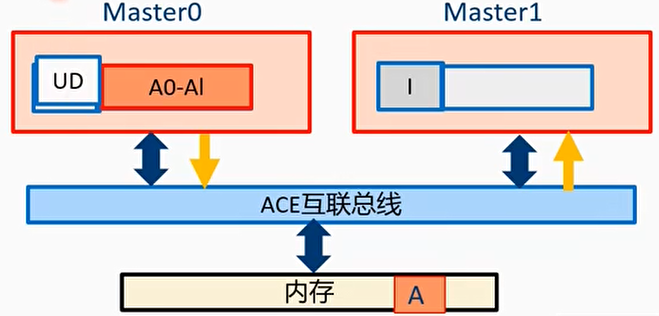

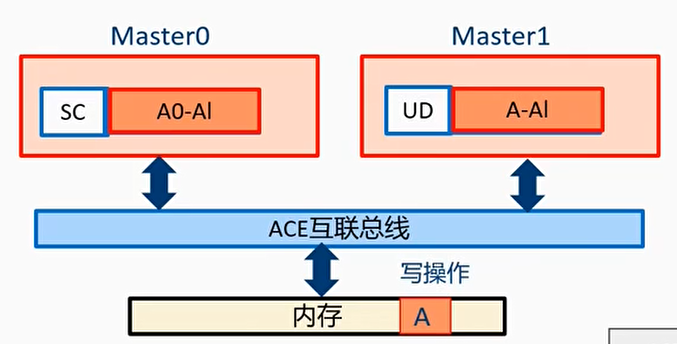

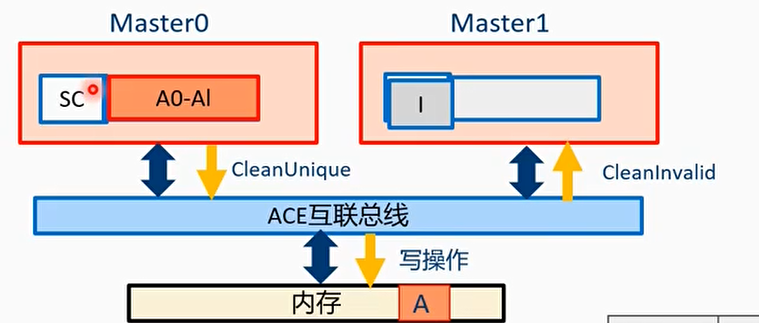

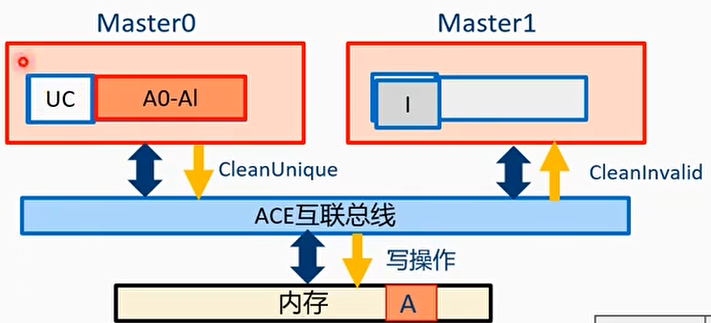

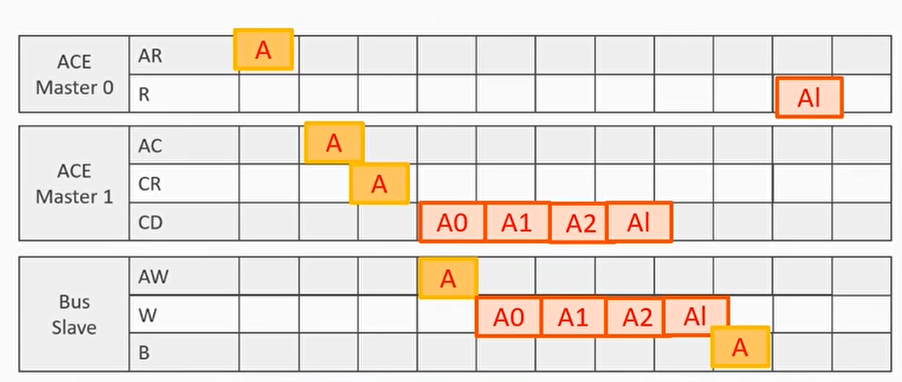

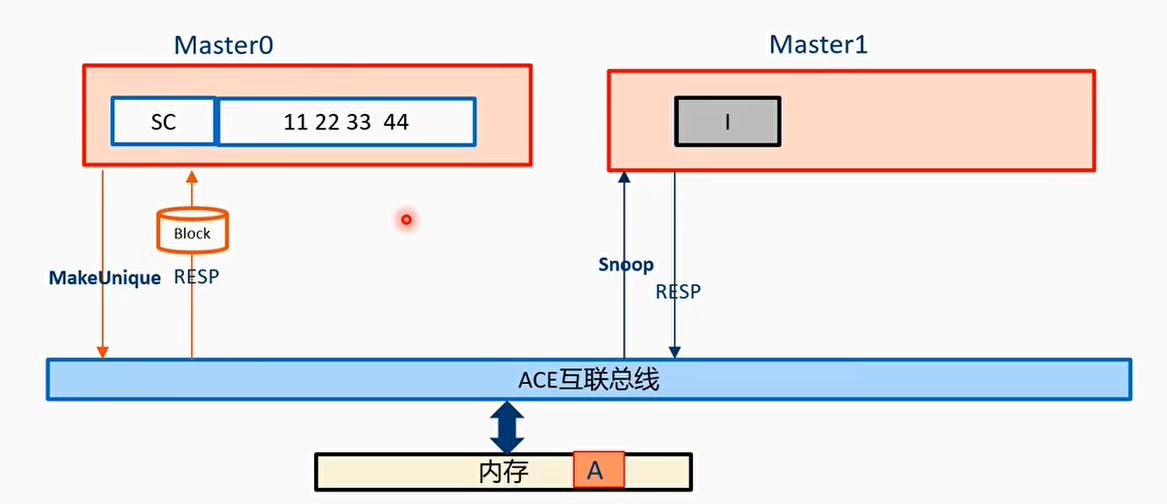

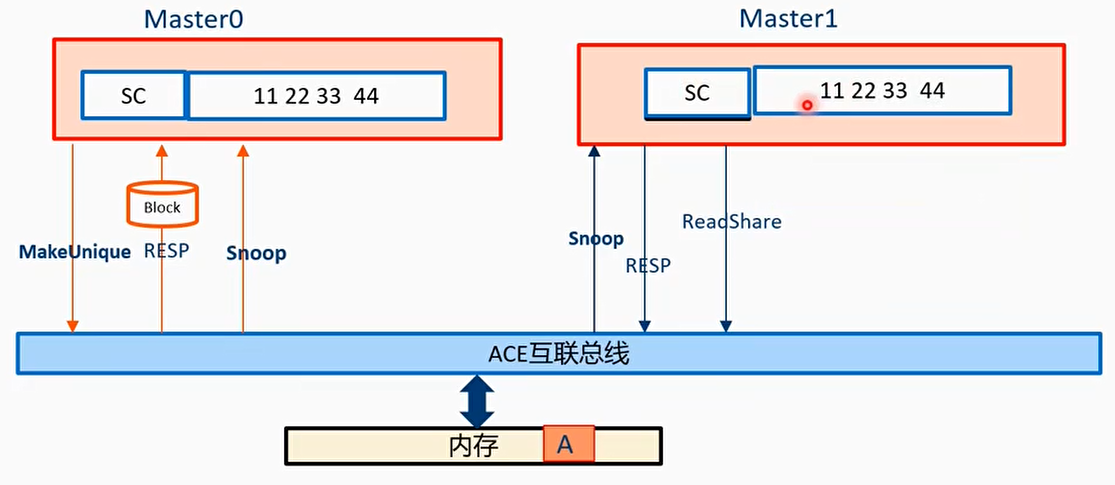

例子3:shareable write 1(full cache line)

例子4:shareable write 2(partial cache line)

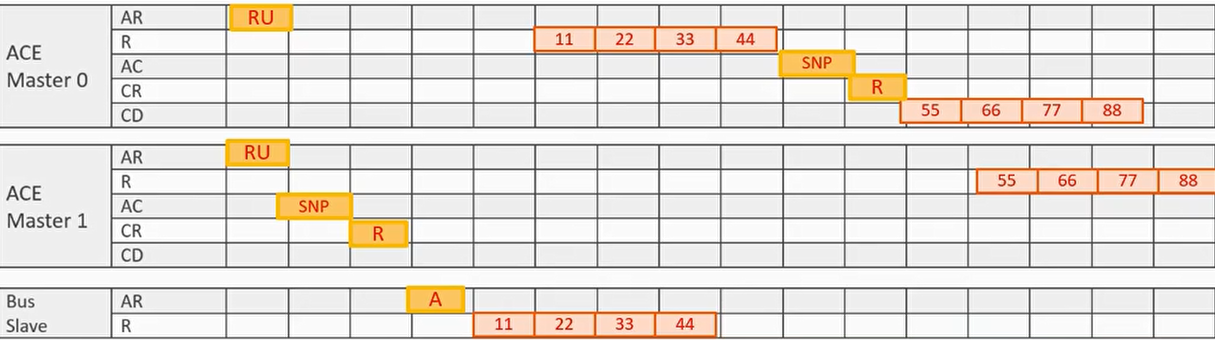

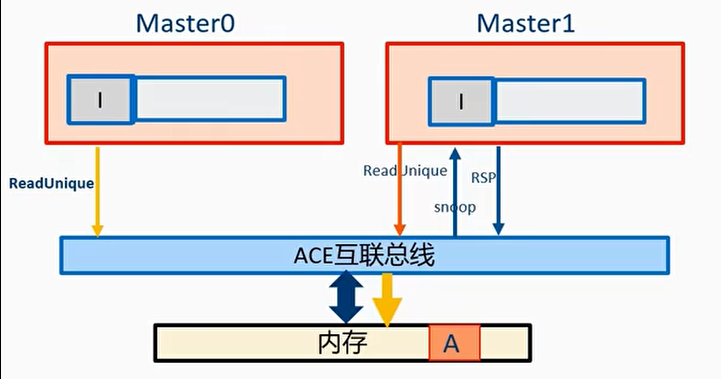

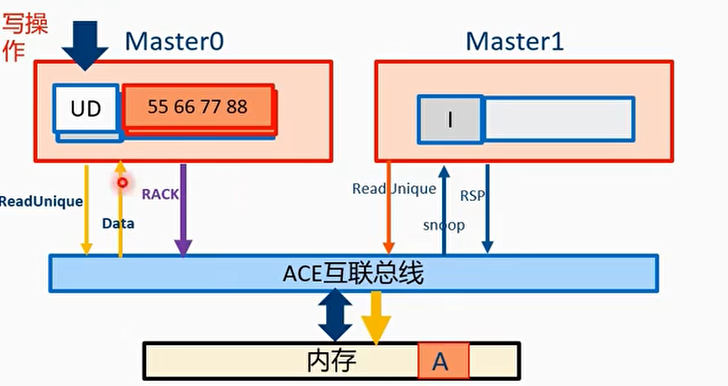

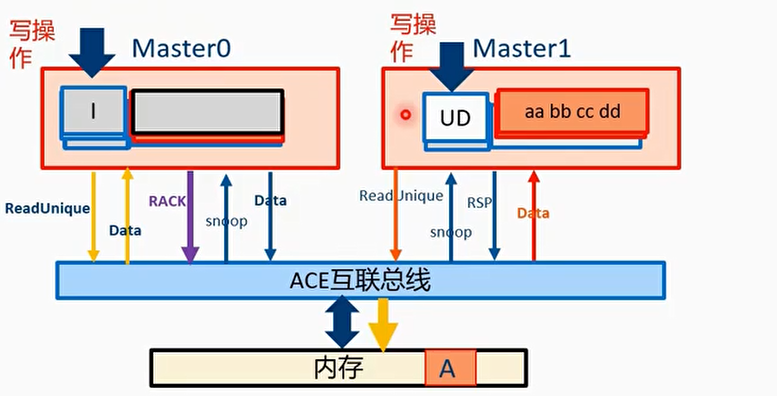

例子5:同时发起ReadUnique写操作

- T0时刻Master0和Master1的cache line状态都是I,地址A的初始化值为0x11223344

- T时刻, Master0和Master1同时发起对地址A写入操作

- Master0想对地址A写入:0x555667788

- Master1想对地址写入:0xaabbccdd

总线会做一个仲裁,处理完一个的请求后再去处理另外一个

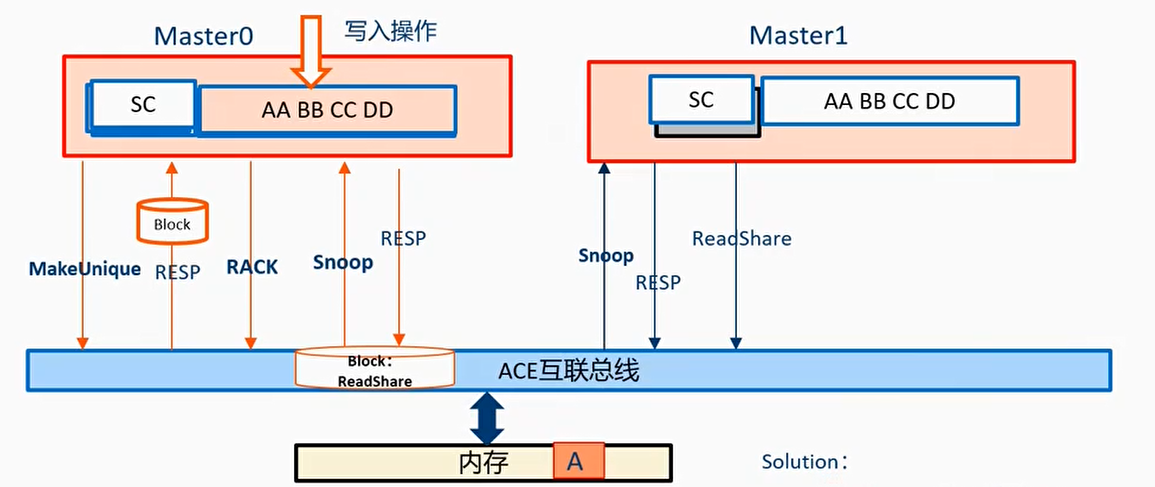

RACK和WACK信号线

- 在例子5中使用了RACK信号线:表示ReadUnique事务已经完成

- 在AXI总线上,支持多个outstanding的传输和乱序传输,不过在ACE中,很有可能会出现cache一致性问题

- RACK信号线用来表示一个读事务已经完成

- WACK信号线用来表示一个写事务已经完成

- 互联总线IP使用RACK/WACK信号线来保证,之前对一个地址的传输事务已经处理完成才能给其他master发送其他transaction的snooping

- 对于读transcation,当RLAST信号拉高之后表明最后一个读transfer完成,然后master才能发送一个read acknowledge信号

- 对于写transcation,当write response channel发送response握手之后,master才能发送WACK信号

例子6:RACK信号线的使用-问题引入

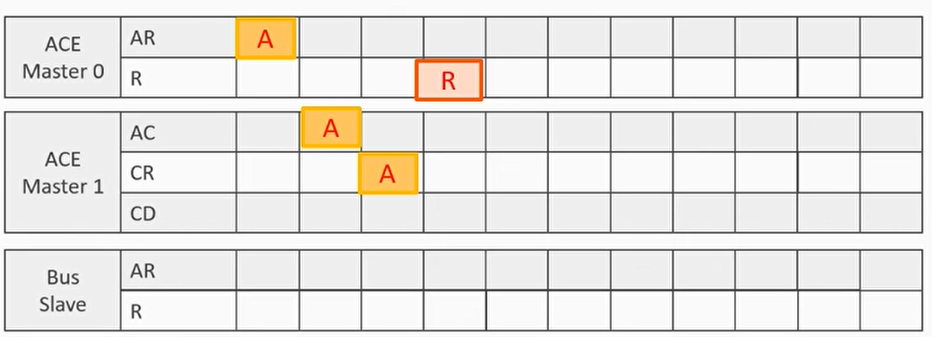

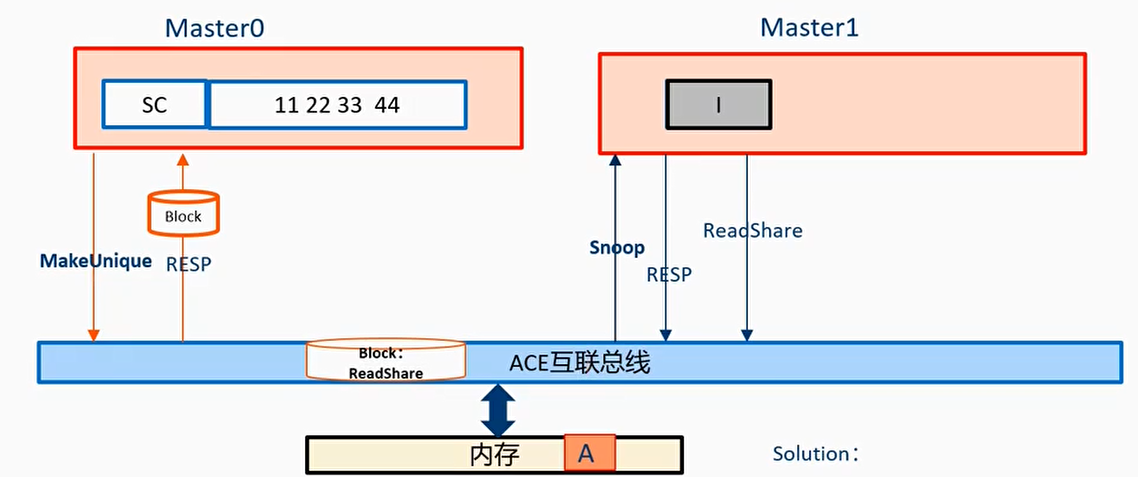

T0时刻:Master0和Master1的cache line状态都是SC

T1时刻:Master0想对地址A数据改写为:0xAABBCCDD

T2时刻:Master1对地址A进行读操作

Root Cause

Master1发起ReadShared事务的时候,master1以为前面的master0的MakeUnique事务已经完成了,但是实际上它是blocking在某个中间的状态,还没有完成

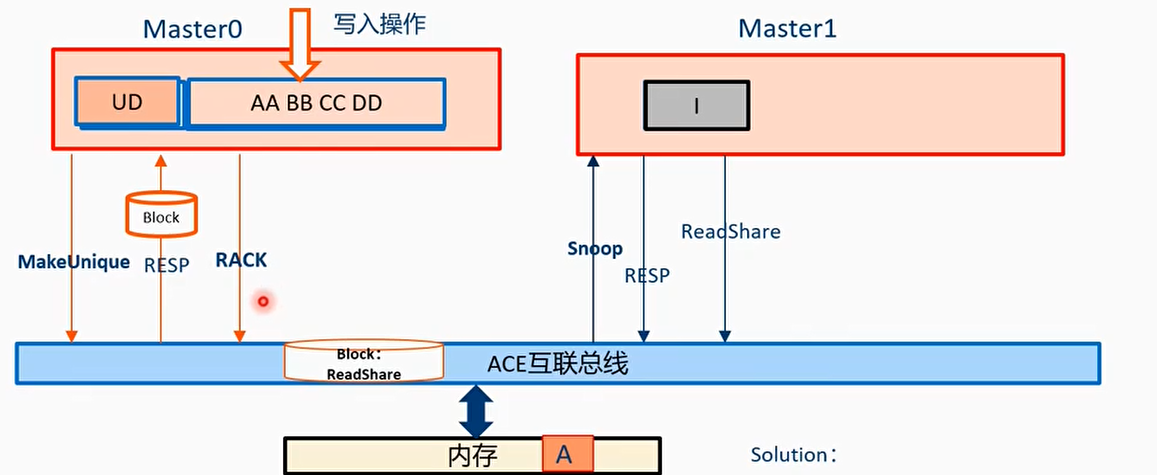

例子6:RACK信号线的使用-问题解决

Solution:Master0使用RACK信号来告诉总线IP:MakeUnique事务已经完成了,总线才能发起其他的snoop相关的事务

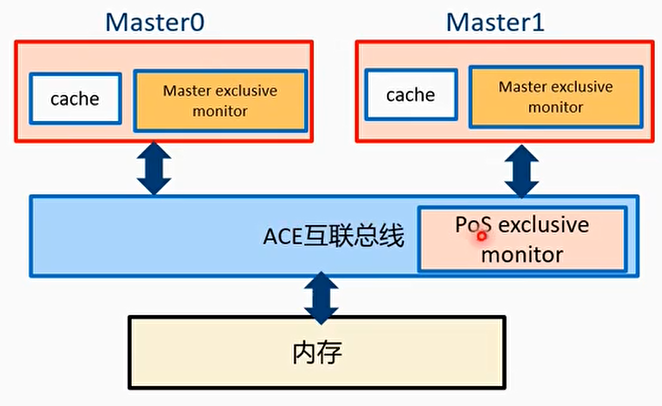

exclusive access

Exclusive access的流程

- 执行exclusive load

- 计算

- 执行exclusive store

- 如果有其它master对这个地址写操作,fail

- 如果没有其他master对这个地址写操作,success

对于Non-shareable和System Shareable内存地址进行exclusive access,行为与AXI一样

对于inner share和outer share内存

- Master exclusive monitor保证在exclusive load之后,没有其他master来写这个地址

- 总线互联的PoS exclusive monitor实现访问序列化

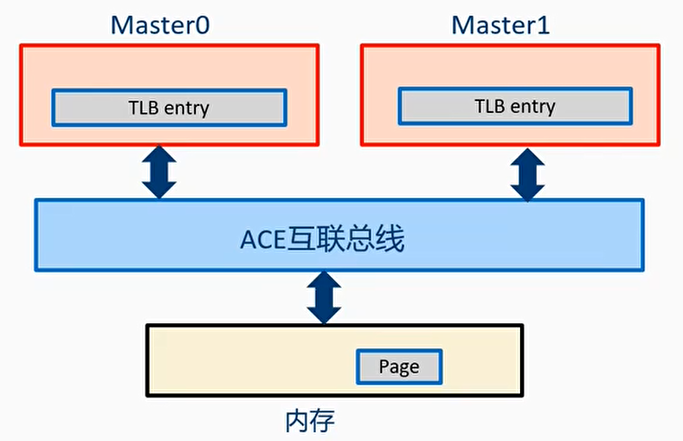

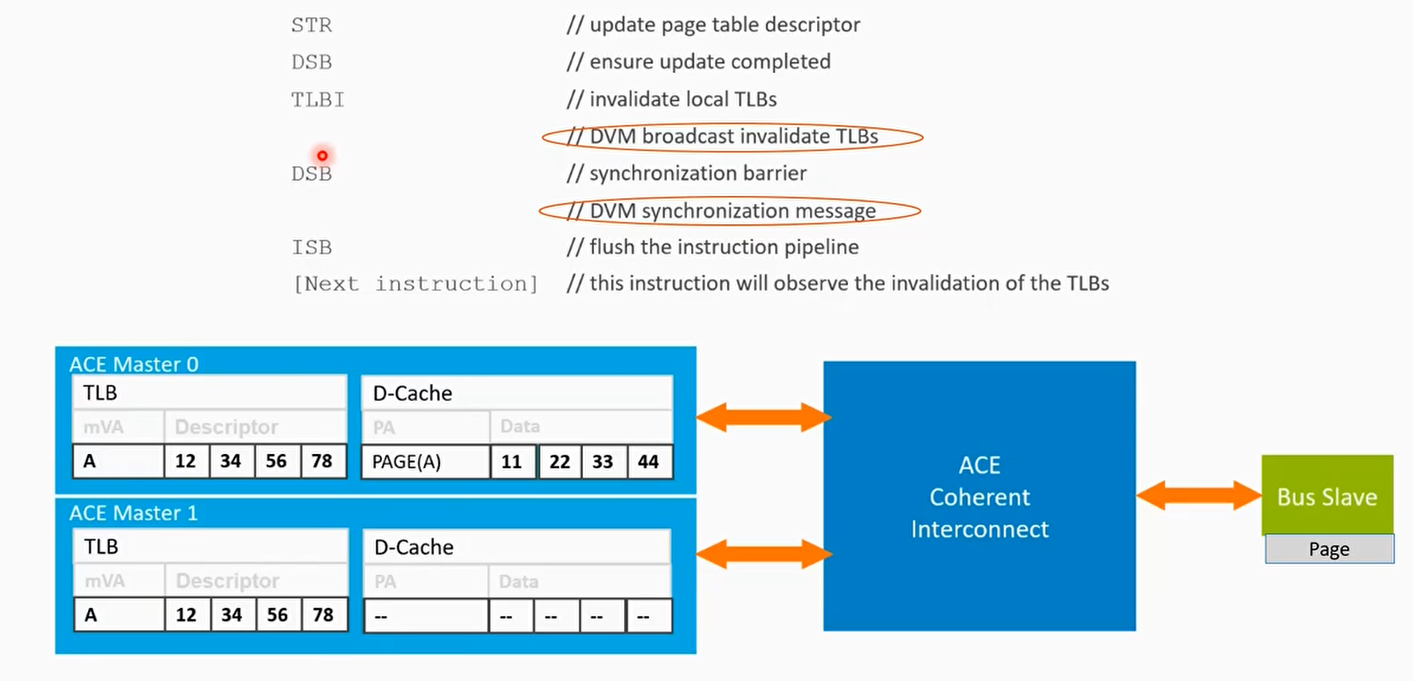

DVM(Distributed Virtual Memory)

- 发送广播到其他master:

- TLB invalidate

- Branch Predictor Invalidate

- Physical Instruction Cache Invalidate

- Virtual Instruction Cache Invalidate

- Synchronization

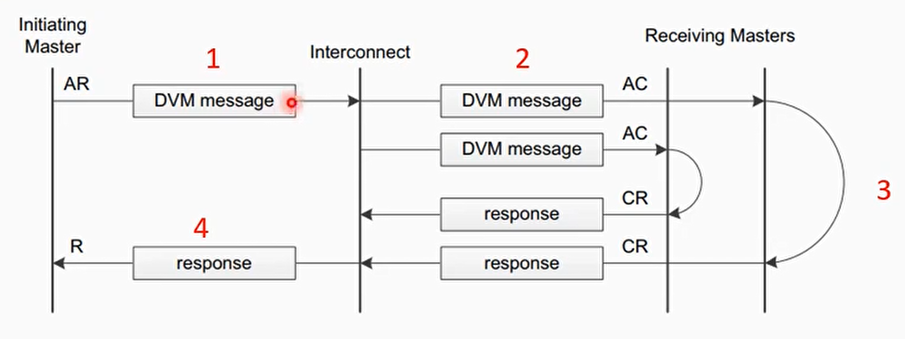

DVM传输事务-DVM message transactions

DVM message事务处理流程:

- Master通过read address channel发送DVM message请求

- 总线收到后,发送snoop到其他master上

- 其他master收到后,通过snoop response channel回应

- 总线收集所有的回应之后,给initiating master通过read data channel发送一个回应包

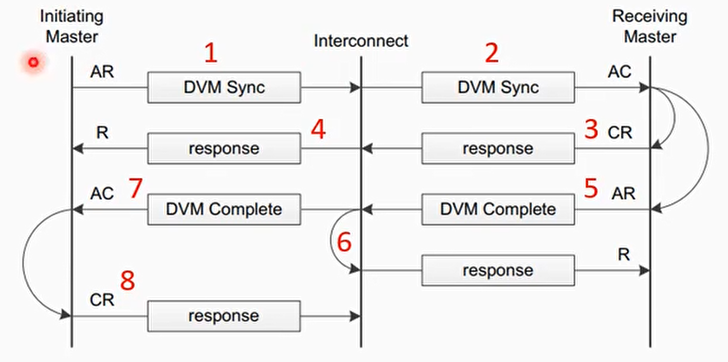

DVM传输事务-DVM Synchronization and DVM Complete transactions

DVM sync 和 complete 事务处理流程:

- Initiating master 通过 read address channel 发出 DVM 同步请求

- 总线收到后,给其他 master 发送 snoop 广播

- 其他 master 收到后,通过 snoop response channel 发送回应。

- 总线收集完所有回应包之后,通过 read data channel 给 initiating master 发送回应包。

- 每个参与的 master 当完成了 TLB invalidation 之后,通过 read address channel 发送一个 DVM complete 事务。

- 总线收到 DVM complete 之后,立马给 master 回应。

- 当总线收集完所有参与 masters 的 DVM complete 事务之后,通过 snoop address channel 给 initaiting master 发送 DVM complete。

- Initiating master 通过 snoop reponse channel 回应总线。

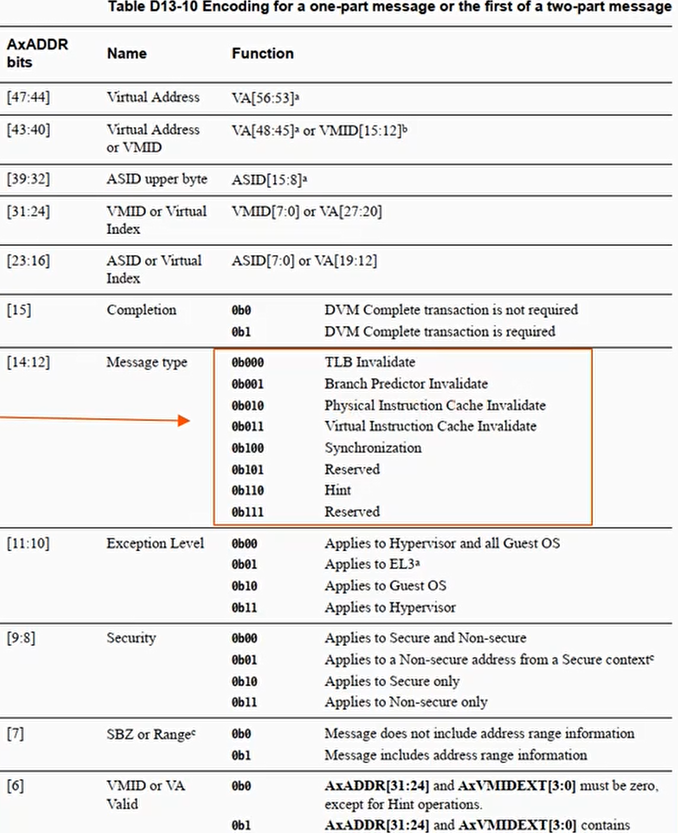

DVM message组包

对AxADDR不同的封装来实现不同的指令,例如TLBI

例子:修改PTE

ACE-Lite

- ACE-Lite应用在不需要参与系统缓存一致性的硬件设备,例如没有本地cache的硬件设备

- GPU

- SMMU

- ACE-Lite支持的事务

- Non-coherent事务:ReadNoSnoop,WriteNoSnoop

- 部分的coherent事务:ReadOnce,WriteUnique,WriteLineUnique

- Cache维护事务:CleanShared,CleanInvalid,MakeInvalid

ACE-Lite + DVM组合

ACE-Lite+DVM应用场景

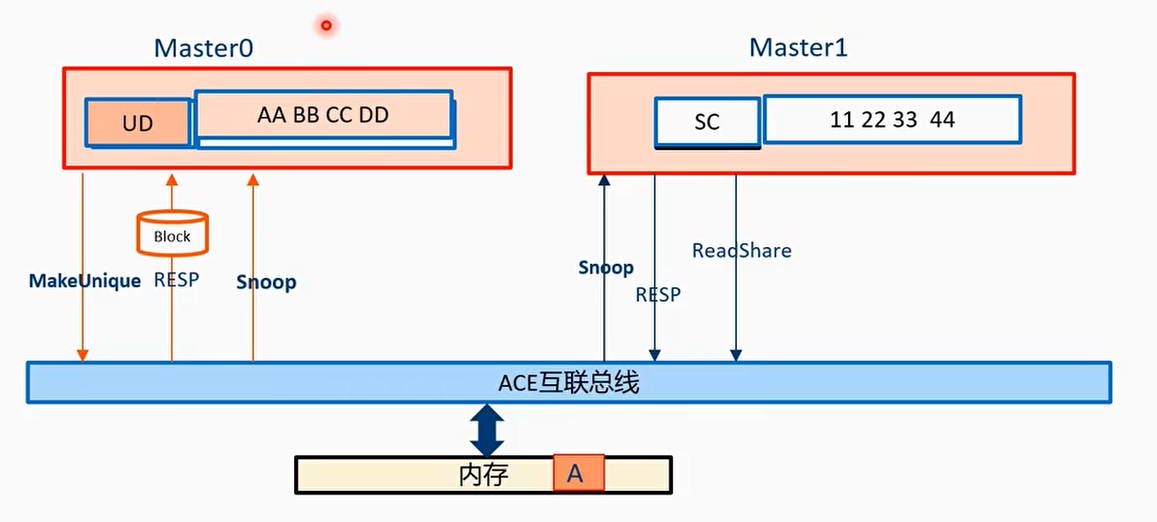

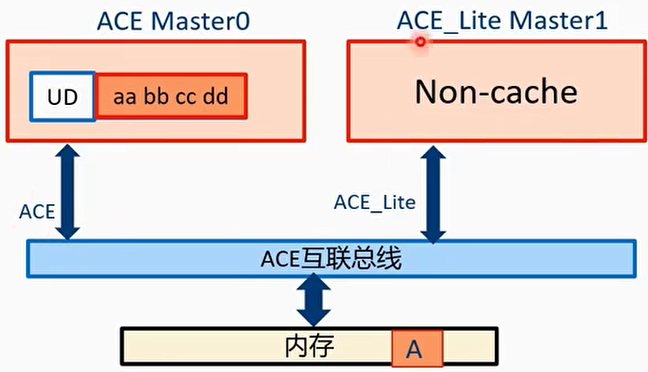

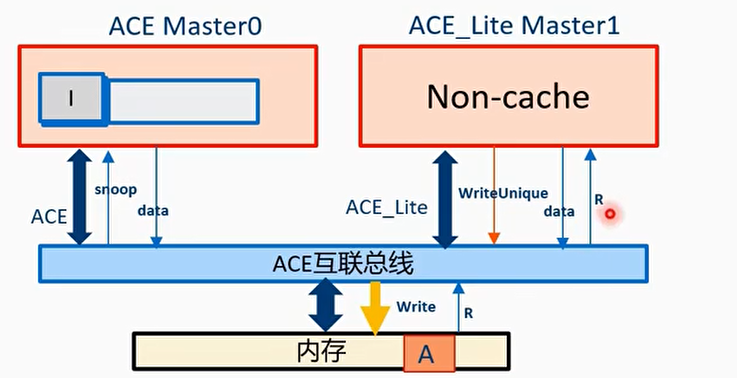

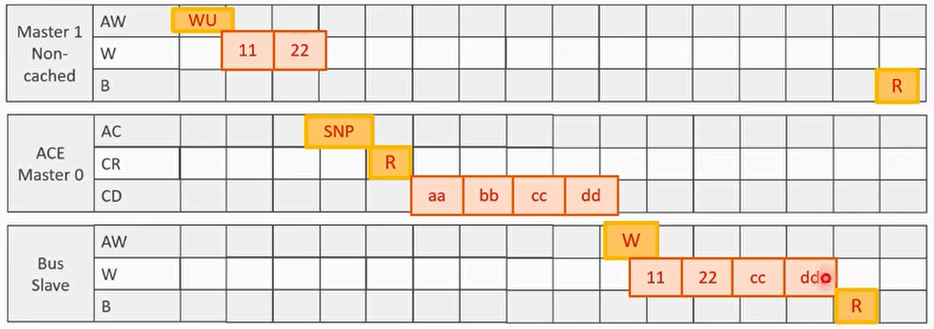

例子:ACE_Lite master执行partial write

- T0时刻:Master0上cache line的状态为UD,假设cache line的值为:aa bb cc dd

- T1时刻:master1往地址A执行partial cache line write操作,往里写入11 22